Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

01> 49П55

Союа Ссеетскнк

Социалистнческнк

Реслублнк (61) Дополнительное к авт. свид-ву (22) Заявлено 04.06.74 (21) 2032222,. 18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.11.75. Бюллетень ¹ 41

Дата опубликования описания 02.02.76 (51) М. Кл. G llс 11/40

Государстееннык комитет

Совета Министров СССР аа делам нзооретеннй н открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

А. В. Ковалев и П. Г. Грицаенко

Таганрогский радиотехнический институт (71) Заявитель (54) ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

Изобретение относится к области вычислительной техники и может быть использовано в оперативных запоминающих устройствах

ЭЦВМ.

Известен запоминающий элемент (ЗЭ) на основе одного биполярного и двух полевых транзисторов со структурой металл-диэлектрик-полупроводник (МДП-транзисторов), способный самовосстанавливать предыдущее состояние при импульсном напряжении пп- 10 тания.

Недостатками такого запоминающего элемента являются высокая критичность к разбросу параметров элементов и низкое быстродействие. 15

Целью изобретения является снижение критичности к разбросу параметров элементов, т. е. повышение надежности работы, и повышение быстродействия ЗЭ.

Поставленная цель достигается тем, что эмиттер биполярного транзистора соединен с истоком первого МДП-транзистора, сток которого подключен к первой шине питания, а база биполярного транзистора подключена к третьей шине питания.

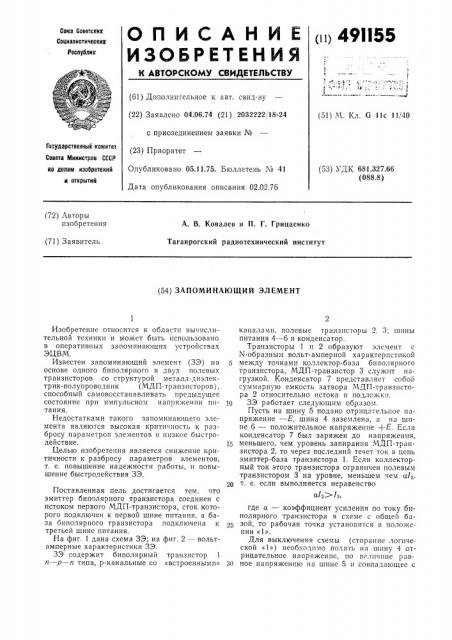

На фиг. 1 дана схема ЗЭ; на фиг. 2 — вольтамперные характеристики ЗЭ.

ЗЭ содержит биполярный транзистор 1 п — р — и типа, р-канальные со «встроенными» 30 каналами, полевые транзисторы 2. 3, шины питания 4 — 6 и конденсатор.

Транзисторы 1 и 2 образуют элсмент с

N-образным вольт-амперной характеристикой между точками коллектор-база биполярного транзистора, МДП-транзистор 3 служит «агрузкой. Конденсатор 7 представляет собой суммарную емкость затвора МДП-транзистора 2 относительно истока и подложки.

ЗЭ работает следующим образом.

Пусть на шину 5 подано отрицательное напряжение — Е, шина 4 заземлена, а на шине 6 — положительное напряжение +E. Если конденсатор 7 был заряжен до напряжения, меньшего, чем уровень запирания МДП-транзистора 2, то через последний течет ток в цепь эмиттер-база транзистора 1. Если коллекторный ток этого транзистора ограничен полевым транзистором 3 на уровне, меньшем чем а12, т. е. если выполняется неравенство а 2) 3 где а — коэффициент усиления по току 6«полярного транзистора в схеме с общей базой, то рабочая точка установится в положении «1».

Для выключения схемы (стирание логической «1») необходимо подать на шину 4 отрицательное напряжение, по гелпчине равное напряжению на шине 5 и совпадающее с

491155

50 ним по времени, а на шину б --- положительное напряжение +Е. В этом случае разность потенциалов в эмиттерно-базовой цепи транзистора 1 близка к нулю, токи эмпттера и коллектора падают, потенциал на емкости возрастает по мере заряда ее током полевого транзистора 3 до напряжения +Е на шинс б.

Если напряжение на шине 4 вновь установить равным нулю, схема остается в выключенной (логический «0»), так как МДП-транзистор 2 закрыт высоким потенциалом коллектора (напряжение на конденсаторе 7 близко к +-Е), следовательно, транзистор 1 тоже закрыт. Открытый МДП-транзистор 3 исключает разряд емкости током утечки биполярного транзистораа.

Запись логической «1» осуществляется путем разряда конденсатора 7 через транзистор

3 при подаче пулевого потенциала па шину 6, совпадающего по времени с отрицательным потенциалом на шипе 5 и нулевым на шине 4.

Как только потенциал на конденсаторе 7 опустится ниже порога запирания МДП-транз:Iстора 2, последний открывается, что приво IIII к лавинообразному процессу открывания транзисторов 1 и 2 и быстрому разряду конденсатора. При этом схема переходит в открытое состояние, соответствующее логической «1».

Пребывание схемы в одном из устойчивых состояний или переход из одного состояния в другое возможен как при статическом, так и при импульсном напряжении питания, подаваемом на шину 5. В этом случае напряжение на шине 5 должно изменяться от положительного уровня +2Е до отрицательного напряжения — Е. Если в схеме была записана логическая «1», то напряжение «а конденсаторе было бы близко к пулю. Потенциал

+2Е на шине 5 удерживает транзисторы 1 и

3 в запертом состоянии и не допускает заряд конденсатора 7 от потенциала +Е па выводе б. С приходом импульса питания --Е на шину 5 открываются все транзисторы схемы, и она остается в открытом состоянии. (ледовательно, подтверждается предварительное состояние схемы: логическая «1». Если в схеме записан логический «0», то папря;кение на конденсаторе 7 близко к +Е, транзистор 2 открыт потенциалом +2Е па шине 5, однако транзистор 1 заперт этим же потенциалом, 5

30 поэтому заряд конденсатора 7 сохраняется неизменным. Приход отрицательного импульса

2Е на шину 5 запрещает протекание тока через транзистор 2, и схема остается в закрытом состоянии. Таким образом, подтверждается предварительное состояние схемы: логический «0».

Импульсный режим питания шины позволяет значительно уменьшить потребляемую

»ощность при хранении логической «1».

Считывание информации осуществляется путем подачи отрицательных импульсов считывания — E на шину 5. Импульсы считывания располагаются в интервале между импульсами питания. Сигнал, характеризующий состояние ЗЭ, снимается па шине 4 (или 6) в виде тока илп напряжения при подключении нагрузочпого резистора в цепь шины 4 (пли 6).

Задание тока эмиттера биполярного транзистора, (а не тока базы, как в прототипе) снижает критичность ЗЭ к разбросу коэффициента усиления по току транзистора в схе:»e с общей базой (а). Известно, что разброс в зна ениях $, где P — коэффициент усиления транзистора по напряжению, во много раз превышает разброс в значениях а. Поэтому предлагаемая схема меньше критична к разбросу параметров элементов.

Кроме того, задание тока эмиттера позволяет значительно уменьшить глубину насыщения биполярного транзистора, что увеличивает быстродействие схемы.

Предмет изобретения

Запоминающий элемент, содержащий биполярный транзистор МДП и транзисторы, затвор первого из которых и сток второго саед.шены с коллектором биполярного транзистора, затвор второго МДП-транзистора соединен с первой шиной питания и сток второго

МДП-транзистора — со второй шиной питания, отл и ч а и щи йся тем, что, с целью повышения на,нежности работы элемента и его быстродействия, в нем эмиттер биполярного трапзп тора соединен с истоком первого

МДП-транзистора, сток которого подключен к первой шине питания, а база биполярного транзистора подключена к третьей шине питания.

Фиг У

Фиг 2

Составитель P. Яворовская

Техред А. Камышникова Корректор Т. Добровольская

Редактор Л. Утехина

Типография, гр, Сапунова, 2

Заказ 40/13 Изд. № 70 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4 5