Постоянное запоминающее устройство с блокировкой неисправных запоминающих элементов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (н1 49И58

Союз Советских

Сокиалиотических

Ресаублик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.05,74 (21) 2026109 18-24 (51) М. Кл. G 11с 17. 00 с присоединением заявки №

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (23) Приоритет

Опубликовано 05.11.75. Бюллетень М 41 (53) УДК 681.327.66 (088.8) Дата опубликования описания 02.02.76 (72) Авторы изобретения

О. А. Терзян и Л, М. Чахоян (71) Заявитель (54) ПОСТОЯ Н НО Е ЗА ПОМИ HAIOI ЕЕ УСТРОЙ СТВО

С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЗАПОМИНАЮЩИХ

ЭЛ ЕМЕНТОВ

Изобретение относится к области вычислительной техники и может быть использовано в

ЦВМ.

Известны ЗУ с блокировкой неисправных запоминающих элементов (ЗЭ), содержащие регистр адреса, дешифратор кода адреса, накопитель, регистр считываемой информации, блок хранения кода неисправного разряда и дешифратор кода адреса неисправного разряда.

Недостатками этих ЗУ являются их сложность и малое быстродействие.

Целью изобретения является упрощение устройства и повышение его быстродействия.

Эта цель достигается путем того, что устройство содержит и дешифраторов кода неисправного разряда группы информационных разрядов, входы которых соединены с блоком хранения кодов неисправных разрядов, а выходы со входами соответствующих информационных разрядов регистра информации.

В предлагаемом ПЗУ запоминающий массив накопителя условно делится на и групп таким образом, чтобы в каждой группе любого слова было бы не более одного неисправного ЗЭ.

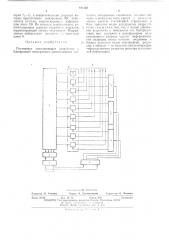

Блок-схема ПЗУ с блокировкой неисправных ЗЭ приведена на чертеже.

ПЗУ содержит регистр адреса 1, дешифратор кода адреса 2, накопитель 3, регистр считываемой информации 4 с информационными разрядами 5, блок хранения кодов неисправных разрядов 6, и дешифраторов кода неисправного разряда группы информационных

5 разрядов 7> — 7 .

Входы регистра адреса 1 и блока G соединены с шинами кода адреса 8. Выходы регистра адреса 1 соединены через дешифратор кода адреса 2 с накопителем 3, выходы которого

10 соединены с входами информационных разрядов 5 регистра информации 4. Выходы блока 6 соединены с входами соответствующих дешифраторов 7 — 7», выходы которых подключены к входам соответствующих информа15 ционных разрядов.

ПЗУ работает следующим образом.

Код адреса 8 одновременно поступает на регистр информации 4 и блок 6.

Прп обращеннн по исправному адресу

20 ПЗУ работает как обычно: выбранное с помощью дешифратора кода адреса 2 слово из накопителя 3 поступает на регистр информации 4, а затем на выходные шины 9. Прн этом на выходах дешифраторов 7 — 7» коррек25 тирующая информация отсутствует.

При обращении к адресу с неисправными

ЗЭ выборка из накопителя 3 производится аналогично. Однако в этом случае из блока 6 на входы дешифраторов 7> — 7„подаются коды

50 неисправных разрядов. На выходах дешнфра491158

Предмет изобретения

Й с!

Состс iiirr.:L 1Ск Роз и- та ls 1 екред A. (ав!! !ии:икова 1;орректор Е. Х-.,!елева

Редактор Л. Утехи!!а

Заказ 40/16 Изд. № 70 Тираж 6зт8 Подписное

Ц!1ИИПИ Государствен!го!.o комитета Совета 1ииистров СССР ио дс::а..- !с!с:;рсirili; I о:крв!!! и

Л!оскаа,,К-86, à,киска!! зао., д, 4 5 торов 7! — 7n, в инфорк!а!циоп! ых разрядах которыx присутствуют пеисправпыа 33, появляются сигналы, коррсктпрующп информацию этого 3Э. На выходах дешие .р.-.торов, соответствующих группам исправп...: разрядов, корректирующий сигпа;! отсутствует. Исправленная информация поступаст:; вы YG.!пые шины 9.

Постоянное запоминающее устройство с блокировкой неисправных запоминающих элел!сп го!!, со;!вf) хка1цес !;с!копите. lь, согд!Ипе! ы Й срез дешифратор кода адреса с ре!! с! l адреса, регистр с :итываемой и;!форм ац1,:! и бло!, храпения кодоз пепспран1ых разря, .-,в, 6 отлп . аю цсеся тем, ято, с целью упрощения устройства и повышения его быстродействия, оно содержит п,дешифраторов. кода неисправного разряда груг,пы информацпон-!!ых разрядов, входы к"торых соединены с

10 блоком храпения кодов неисправных разрядов, а выходы — со входами соответству!ощпх информационных разрядов регистра с".итываемой информации.