Устройство для выделения рекуррентного синхросигнала

Иллюстрации

Показать всеРеферат

r (-p=(->

ОП И СA-Й=Й

ИЗОБРЕТЕН H SI

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 49I 22(0

Со(оз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.04.73 (21) 1904217/26-9 с присоединением заявки № (23) Приоритет

Опубликовано 05.11.75. Бюллетень № 41

Дата опубликования описания 05.02.76 (51) М. Кл. Н 04l 7/04

Н 03k 5/00

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 681.327.8 (088.8) (72) Автор изобретения

И. Ф. Хомич (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ РЕКУРРЕНТНОГО

СИНХРОСИГНАЛА

Изобретение относится к технике связи, может использоваться для помехоустойчивой синхронизации систем передачи двоичной информ ации.

Известно устройство для выделения рекуррентного синхросигнала, содержащее анализатор рекуррентной последовательности, накопитель и последовательно соединенные счетчик ошибок и селектор синхросигнала.

Цель изобретения — повышение помехоустойчивости выделения синхросигнала.

В предлагаемом устройстве между одним выходом анализатора рекуррентной последовательности и входом счетчика ошибок введен селектор ошибок, а между другим выходом анализатора рекуррентной последовательности и входом селектора синхросигнала — блок запрета, к одному из входов которого подключен через накопитель выход селектора ошибок.

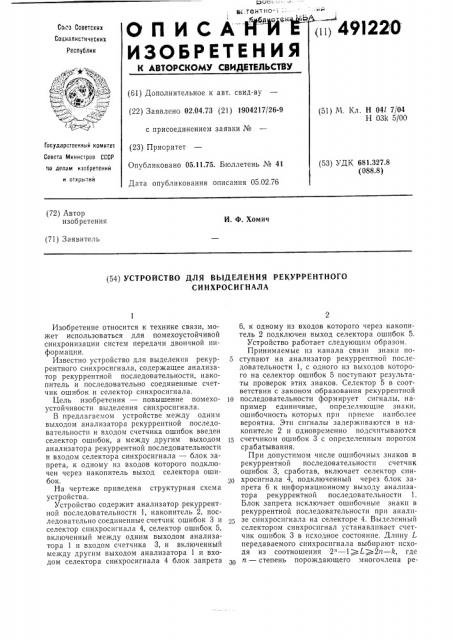

На чертеже приведена структурная схема устройства.

Устройство содержит анализатор рекуррентной последовательности 1, накопитель 2, последовательно соединенные счетчик ошибок 3 и селектор синхросигнала 4, селектор ошибок 5, включенный между одним выходом анализатора 1 и входом счетчика 3, и включенньш между другим выходом анализатора 1 и входом селектора синхросигнала 4 блок запрета

6, к одному из входов которого через накопитель 2 подключен выход селектора ошибок 5.

Устройство работает следующим образом.

Принимаемые из канала связи знаки по5 ступают на анализатор рекуррентной последовательности 1, с одного из выходов которого на селектор ошибок 5 поступают результаты проверок этих знаков. Селектор 5 в соответствии с законом образования рекуррентной

)О последовательности формирует сигналы, например единичные, определяющие знаки, ошибочность которых при приеме наиболее вероятна. Этп сигналы задерживаются в накопителе 2 и одновременно подсчитываются

)5 счетчиком ошибок 3 с определенным порогом срабатывания.

При допустимом числе ошибочны < знаков в рекуррентной последовательности счетчик ошибок 3, сработав, включает селектор синхросигнала 4, подключенный через блок запрета 6 к информационному выходу анализатора рекуррентной последовательности 1.

Блок запрета исключает ошибочные знаки в рекуррентной последовательности при анализе синхроспгнала на селекторе 4. Выделенный селектором синхросигнал устанавливает счетчик ошибок 3 в исходное состояние. Длину L передаваемого синхросигнала выбирают исходя из соотношения 2" — 1) 1.) 2тт — /г, где а — степень порождающего многочлена ре491220

Составитель А. Кузнецов

Техред Е. Подурушина

Корректор Л. Денискина

Редактор Б. Федотов

Заказ 78/12 Изд. № 82 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 куррентной последовательности, /г — длина селектора синхросигнала 4. Порог срабатывания счетчика ошибок 3 выбирают исходя из заданных требований к допустимому числу ошибок в рекуррснтной последовательности.

Предмет изобретения

Устройство для выделения рекуррентного синхросигнала, содержащее анализатор рекуррентной последовательности, накопитель и последовательно соединенные счетчик ошибок и селектор синхросигнала, о т л и ч а ю щ е с с я тем, что, с целью повышения помехоустойчивости выделения синхросигнала, между одним выходом анализатора рекуррентной последовательности и .входом счетчика ошибок введен селектор ошибок, а между другим выходом анализатора рекуррентной последовательности и входом селектора синхросигнала — блок запрета, к одному из входов котоip рого подключен через накопитель выход селектора ошибок.