Устройство для извлечения корня -ой степени

Иллюстрации

Показать всеРеферат

р 49l946

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнх

Соцналнстнчвскнх

Республнк (61) Дополнительное к авт. свид-ву (22) Заявлено 15.10.73 (21) 1963314/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.11.75. Бюллетень № 42

Дата опублико|вания описания 22.04.76 (51) М. Кл. G 06f 7/38

Государственный комитет

Совета Министров СССР (53) УДК 681.325.5 (088.8) по делам изобретений н открытий (72) Авторы изобретения

А. П. Войтер, В. И. Корнейчук, В. П. Тарасенко, А. К. Тесленко и Б. П. Хижинский

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ и-й СТЕПЕНИ

Предлагаемое изобретение относится к области цифровой вычислительной техники и может быть использовано при построении цифровых вычислительных машин.

Известны устройства для извлечения квадратного и кубических корней, содержащие сдвиговые регистры, сумматор, регистр результата, регистр аргумента и блок управления, связанный с регистрами и сумматором.

Недостатком известных устройств является невозможность осуществления на них операции извлечения корня высших степеней.

Предлагаемое устройство отличается тем, что оно содержит (и — 1) сдвиговых регистров (n — 1) сумматоров, сдвиговый регистр начального коэффициента, коммутатор результата и коммутатор младшего коэффициента, первый вход которого соединен с первым выходом блока управления, второй вход — с выходом регистра результата, а выход соединен с первым входом сдвигового регистра начального коэффициента и всех сумматоров, второй вход сдвигового регистра начального коэффициента соединен со вторым выходом блока управления и с первыми входами остальных сдвиговых регистров, связанных двусторонней связью с соответствующими сумматорами; выход младшего разряда i-го сумматора соединен со вторым входом (i+1)-ro сумматора и сдвигового регистра, вторые входы второго сумматора и сдвигового регистра соединены с выходом младшего разряда сдвигового регистра начального коэффициента, выход знакового разряда и-ro сумматора соединен с первым входом коммутатора результата, второй вход которого соединен с третьим выходом блока управления, а выход соединен со входом регистра результата, выход регистра аргумента связан со входом n-ro сумматора.

Это позволяет извлекать корень положительной степени до и включительно путем вычисления и-й степени от искомого числа и сравнения результата с аргументом.

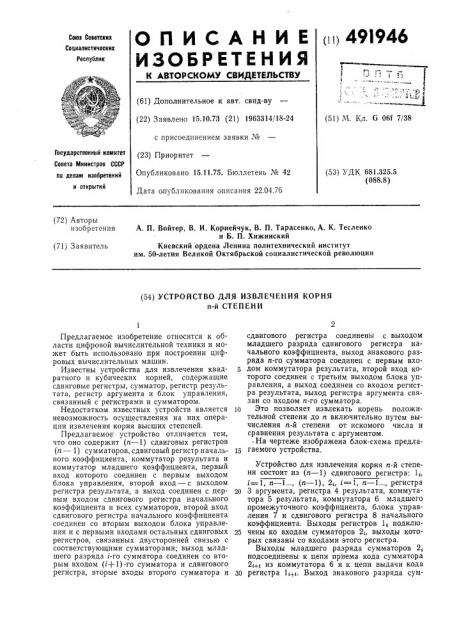

° На чертеже изображена блок-схема предла15 гаемого устройства.

Устройство для извлечения корня и-й степени состоит из (и — 1) сдвигового регистра: l;, i=1, n — 1..., (n — 1), 2,, i=1, n — 1..., регистра

20 3 аргумента, регистра 4 результата, коммутатора 5 результата, коммутатора 6 младшего промежуточного коэффициента, блока управления 7 и сдвигового регистра 8 начального коэффициента. Выходы регистров l; подклю25 чены ко входам сумматоров 2,, выходы которых связаны со входами этого регистра.

Выходы младшего разряда сумматоров 2; подсоединены к цепи приема кода сумматора

2; из коммутатора 6 и к цепи выдачи кода

30 регистра 1т+ь Выход знакового разряда сум491946

0,00000

О, IОП I

О, IОПI

0,00000

О, IОП I

О, IОП I

0,00000

О, IОПI

О, IОПI

0,00000

О, IОП I

О, IОП I

О, IОП I

О, ОIОП

0,00000

О, ОIОП

О,ОIОП

О, IОП I

1,00010 о,оюп

0,00000

О,ОIОП

О, ОIОП

О, IОП I

1,00010

0,00101

О,ООЮ1

0,00000

0,00101

0,10001

1,10П I

1,01000

0,00101

0,00000

0,00101

0,10001

О,ЮП1

1,01000

О,OOIOI

0,00010

0,00001

0,00000

О, IОП I

О, IОП I

0,00101

o, ooooo

0,00101

О,ОПОО

0,00000

О,ОПОО

0,10000

0,00000

0,00010

О,О1ОП

О,ООПО

0,01000

0,00100

0,00101

0,00000

0,00101

0,00001

О, IОП I

О, ПООО

О,ОООП

0,00000

О,ОООП

0,00010

О, IОПI

О, ПОО 1

О,ОПОО

О, IОПI

I OOOII

0,00001

0,00000

О, ОООО1

0,00010

О,ОПОО

0,00000

О,ОПОО

О,10001

О, IОПI

1,01080

0,00000

О, IОПI

О, IОПI

0,00001

О,ООПО

О, IОПI

О, П101

O,IOIOO

О, IОПI

1, ОIОП

О, ОIОП

0,00000

0,10101

О, IОП I

I,ОПОО

0,01ПO

0,00000

О,ОПIО

0,00101

0,00010

0,00001

0,10001

0,00000

0,10000

0,00001

0,10111

О, ПООО

0,00000

0,00000

О, ПООО

0,01000

О,ОП00

О,ООПО

0,00000

0,00000

Номер цикла

1 (2 (О, 1ОП1

О, 1ОШ

0,10100

О,IOIOO

О,1О»О

О, IОПО

0,10000

О, ПООО

0,10000

О, Ю00О

Регистр 4

Регистр 8

0,10100

0,01010

О, IОПI

1,00001

0,00010

0,00001

О, IОПI

О, ПООО

0,00000

0,00000

0,00000

0,00100

0,01010

0,00000

0,01010

О, IОПО

О, ОIОП

О, IОП I

1,00010

0,00100

0,00010

0,00001

3 4

Таблица

0,00010

0,00001

0,00000

0,00001

О,ООП I

О,ОООП

0,00000

О,ОООП

О,ООПО

О,ОООП

0,00001

0,IOI11

О, ПООО

Т аблица

491946

5 матора 2 1 связан со входом коммутатора 5, выходы которого подключены ко входам регистра 4 результата.

Выходы регистра 4 через коммутатор б подсоединены ко входам всех сумматоров и ко входам сдвигового регистра 8 начального коэффициента. Выходы регистра 3 аргумента подключены ко входам сумматора 2„ . Выход младшего разряда сдвигового регистра 8 начального коэффициента подключен к цепи приема кода сумматора 2 из коммутатора, б и к цепи выдачи кода сдвигового регистра 8.

Выходы блока управления 7 связаны со входами цепи выдачи обратного кода регистра 3 аргумента, со входами коммутаторов 5 и б, с цепями сдвига всех сдвиговых регистров и со входами цепи выдачи кода сдвигового регист1„— 1

Работу устройства рассмотрим на примере

5 вычисления у= 0,235.

Перед началом работы аргумент 0,235 заносится в регистр 3 аргумента. Количество разрядов m в регистрах и сумматорах предлагаемого устройства выбирают, исходя из требуемой точности вычисления искомого значения корня. В данном примере положим для

5 оп еделенности m=5. Вычисление 0,235

P длится и циклов, В начале первого цикла схема управления

7 через коммутатор б записывает единицу в первый справа после запятой разряд регистра

8 начального коэффициента, т. е. заносит код

0,10000. Такой же код будет на выходе коммутатора 6 в течение всего первого цикла. В первом такте первого цикла происходит одновременное суммирование на всех сумматорах таким образом, что на сумматоре 2; складывается содержимое сдвигового регистра 1; с кодом на выходе коммутатора б (если на выходе младшего разряда сумматора 2; i— единица или с нулем, когда на выходе младшего разряда сумматора 2; < — Буль).

Сумматор 2 и регистр 11 управляются выходом младшего разряда сдвигового регистра

8 начального коэффициента.

Первый такт заканчивается сдвигом вправо на один разряд содержимого всех сдвиговых регистров. Последующие такты аналогичны описанному.

После окончания всех тактов (в общем случае m(n — 1) тактов) на сумматор 2„, подается содержимое регистра 3 аргумента в дополнительном коде и содержимое сдвигового регистра 1 ь Если результат при этом отрицательный, то в первый справа после запятой разряд регистра 4 результата через коммутатор 5 записывается единица, если же результат положительный — то записывается нуль. В данном примере на регистре 4 будет записан код 0,10000. Содержимое регистра 1 устанавливается на нуль. Этим заканчивается первый цикл вычислений.

4О

55 б

Во втором цикле на сдвиговый регистр 8 через коммутатор 6 подается содержимое регистра 4 результата. Во второй (в и-м цикле в т-й, где m=1, 2, ...5) справа после запятой разряд сдвигового регистра 8 записывается единица, в данном примере будет записан код

0,11000).

После этого следуют такты (в общем случае m(n — 1) тактов), аналогичные описанным выше. После окончания второго цикла содержимое регистра 4 имеет вид 0,10000 и т. д. до окончания пятого цикла, когда в регистре 4 результата будет записан результат вычисле5 ния ф 0,235.

На предлагаемом устройстве можно вычислять корень из чисел, больших единицы. В

П этом случае производят вычисления ) Х,где

Х =Х.2 — "(1, аналогичным способом, что и при Х(1, а запятую в регистре 4 результата по окончании вычислений сдвигают вправо на и

-разрядов, где и выбирают кратным числу и. п

Содержимое регистров в пятом цикле при

5 вычислении ф 0,235 иллюстрирует таблица 1, где обозначены состояния сдвиговых регистров и коды, подаваемые на сумматоры 2; в каждом такте вычислений.

B таблице 2 записаны состояния регистра 4 результата в конце каждого цикла и состояния сдвигового регистра 8 начального коэффициента в начале каждого цикла.

После выполнения всех тактов 5-го цикла выполняется операция 1,11001 .

+0,00110

1,11111

Результат отрицательный и поэтому в пятой справа после запятой разряд регистра 4 результата записываем единицу.

Код в регистре 4 есть результат выполне5 ния операции V0,235=0,10111 =0,719.

Формула изобретения

Устройство для извлечения корня и-и степени, содержащее сдвиговые регистры, сумматор, регистр аргумента, регистр результата и блок управления, связанный с регистрами и сумматором, отличающееся тем, что, с целью расширения сдвиговых функциональных возможностей, оно содержит (и — 1) сдвиговых регистров, (n — 1) сумматоров, сдвиговый ре6О

65. гистр начального коэффициента, коммутатор результата и коммутатор младшего коэффициента, первый вход которого соединен с первым выходом блока управления, второй вход — с выходом регистра результата, а выход соединен с первым входом сдвигового регистра начального коэффициента и всех сумматоров, второй вход сдвигового регистра начального коэффициента соединен со вторым выходом блока управления и с первыми вхо491946

Составитель М. Аршавский

Текред Е. Митрофанова

Редактор Б. Нанкина

Корректор В. Брыксина

Заказ 663/3 Изд. Ко 2031 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 дами остальных сдвиговых регистров, связанных двусторонней связью с соответствующими сумматорами, выход младшего разряда i-го сумматора соединен со вторым входом (1+1) -ro сумматора и сдвигового регистра, вторые входы второго сумматора и сдвигового регистра соединены с выходом младшего разряда сдвигового регистра начального коэффициента, выход знакового разряда и-ro сумматора соединен с первым входом коммутатора результата, второй вход которого соединен с третьим выходом блока управления, а выход

5 соединен со входом регистра результата, выход регистра аргумента связан со входом иго сумматора.