Устройство для обмена информацией между оперативной памятью и процессором

Иллюстрации

Показать всеРеферат

) 49I952

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 18.01.74 (21) 1992831/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.11.75. Б«оллетень ¹ 42

Дата опубликования описания 18.02.76 (51) М. 1 л. G 06f 13/06

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327(088,8) (72) Авторы изобретения

С. Б. Погребинский и В. Д. Вероцкий (71) Заявитель

Ордена Ленина институт кибернетики AH Украинской (4 = — .. (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ МЕЖДУ

ОПЕРАТИВНОЙ ПАМЯТЬЮ И ПРОЦЕССОРОМ

Изобретение относится к области вычислительной техники и, в частности, может быть использовано при проектировании устройств оперативной памяти вычислительных машин.

Известно устройство для обмена информацией между оперативной памятью и процессором, содержащее регистр адреса, блок управления обменом, подключенный к буферным регистрам памяти, буферные регистры процессора.

Недостатком известного устройства является невысокое быстродействие.

Описываемое устройство отличается от известного тем, что оно содержит блок сравне- )5 ния, регистр предыдущего адреса и блок коммутации, входы и выходы которого подключены к соответствующим выходам и входам буферных регистров, а управляющие входы соединены с выходом блока управления обме- 20 ном, к одному из входов которого подключен выход блока сравнения, первый вход которого соединен с выходом регистра адреса и одним из входов регистра предыдущего адреса, второй вход — с выходом регистра предыду- 25 щего адреса, другой вход которого соединен с выходом блока управления обменом.

Эт««отличия позволяют повысить быстродействие устройства.

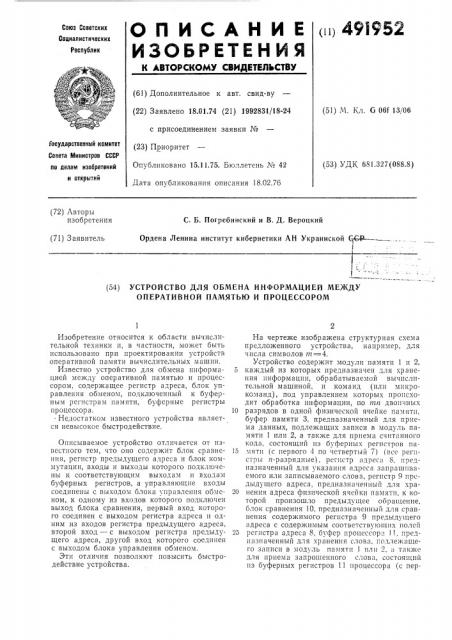

На чертеже изображена структурная схема предложенного устройства, например, для числа символов m=4.

Устройство содержит модули памяти 1 и 2, каждый из которых предназначен для хранения информации, обрабатываемой вычислительной машиной, и команд (пли микрокоманд), под управлением которых происходит обработка информации, по lгггг двоич Iblx разрядов в одной физической ячейке памяти, буфер памяти 3, предназначенный для приема данных, подлежащих записи в модуль памяти 1 или 2, а также для приема считанного кода, состоящий из буферных регистров памяти (с первого 4 по четвертый 7) (все регистры гг-разрядные), регистр адреса 8, пред««азначенный для указания адреса запрашиваемого или записываемого слова, регистр 9 предыдущего адреса, предназначенный для хранения адреса физической ячейки памяти, к которой произошло предыдущее обращение, олок сравнения 10, предназначенный для сравнения содержимого регистра 9 предыдущего адреса с содержимым соответствующих полей регистра адреса 8, буфер процессора ) l. предназначенный для хранения слова, годлежащего 3««IIHcH B мод ль памяти 1 и 1i«2, а также для приема запрошенного слова, состоя«ций из буферных регистров 11 процессора (c пер491952 вого 12 по че-.всртый 15) (все регистры и-разр..д;1ь =,, 0;Ioi< Ko:.i:,I тации 16, Iipp+HaaHBHeHьп для передa÷ii слова, подлежащего записи

n»а, я.-ь, 1,з буфера процессора 11 в некоторь .с гз буферных регистров памяти 4--7 или o гс б, oop!Inie ре1пстры памяти 4 — 7, а такд.-;; н ре1а 111 запрон1епнoio слова, храняН1сгося в нскоторь;х из буферных регистров

;.ы.яти 4--7 в буфер процессора 11, блок 17 у 1равле11гii об 1ено.,1. предназначенный для

,г равлепия î5ñ,сном информацией мс>кду буфс1:о.;: ., роцсс ора,1 и модулями памяти 1 и п соответствии с адресом запрашиваемого ил". записываемого слова Ii кодом операции обра цспия ., 1амятп.

I ia:1ертежс приведена Одна из Возможных структур!Ых схем блока коммутации 16, В соответствии с которой он состоит из первой

18 и второй 19 ступеней коммутации, предназ:;а енных для совместно"o переключения кодовых шпн, связывающих буфер памяти 3 и буфер процессора 11.

В общем случае количество ступеней коммутации может быть произвольным. Блок коммутации 16, состоящий из Й ступеней ком:,, та1111Н, обес1;ечнвает передачу слов, длина

1.ого.ь - равна 2 и-двоичных разрядов, где

1=1, с., В состав первой ступени коммутации 18 входят гервьш 20 и второй 21 блоки переключения, в состав второй ступени коммутации

19 — первый 22, второй 23, третий 24 и четвсртьш 25 блоки перекл1очения. Количество блоков переключения в любой ступени коммутации равно 2, где i — номер ступени коммутации.

Блоки переключения 20 — 25 предназначены для выполнения следующих функций в режиме записи.

Блок переключения 20 служит для подключения выходов первого буферного регистра

12 по входам первого 22 и третьего 24 блоков

1.:ереключе III I второй ступени коммутации 19.

Блок псрекл1очения 21 предназначен для подкгпо ения выходов первого 12 или второго буферного регистра 13 процессора ко входам второго п четвертого блоков переключения 23 и 25 второй ступени коммутации 19.

Блок перекгночения 22 служит для подклю;е;:ия выходов первого блока переключения

20 первой ступени коммутации 18 ко входам пер,oio буферного регистра памяти. Блок перек.по IcIIIHI 23 используется для подключения вь1ходов второго блока переключения 21 первой ступени коммутации 18 ко входам второго буферного регистра памяти 5. Блок nepaid. iIo IeI IIII 24 предпазна io;I ния выходов третьего буферного регистра 14 процессора или первого блока переключения

20 первой ступени коммутации 18 ко входам третьего буферного регистра памяти 6. Блок переключения 25 служит для подключения выходов четвертого буферного регистра 15 процессора или второго блока переключения

21 первой ступени коммутации 18 ко входам четвертого буферного регистра памяти 7.

В режиме чтения из па.",1яти блоки переключения 20 — 25 служат для выполнения следующих функций: блок переключения 22 — для подключения выходов первого буферного регистра памяти

4 ко входам первого блока переключения 20 первой ступени коммутации 18; блок переключения 23 — для подключения выходов второго буферного регистра памяти 5 ко входам второго блока переключения 21 первой ступени коммутации 18; блок переключения

24 — для подключения выходов третьего буферного регистра памяти 6 ко входам третьего буферного регистра 14 процессора или первого блока переключения 20 первой ступени коммутации 18; блок переключения 25— для подключения выходов четвертого буферного регистра памяти 7 ко входам четвертого буферного регистра 15 процессора или второго блока переключения 21 первой ступени коммутации 18; блок переключения 20 — для подключения выходов первого блока переключения 22 или третьего блока переключения 24 второй ступени коммутации 19 ко входам первого буферного регистра 12 процессора; блок»ерсхлючения 21-- для подключения выходов второго блока переключения 23 или четвертого блока переключения 25 второй ступени коммутации 19 ко входам первого 12 или второго буферного регистра 13 процессор а.

Входы и выходы блока коммутации 16 подключены к соответствующим выходам и входам буферных регистров 4 — 7 и 12 — 15, а управляющие входы блока 16 соединены с выходом блока 17 управления обменом, к одному из входов которого подключен выход блока сравнения 10, первый вход которого соединен с выходом регистра адреса 8 и одним из входов регистра 9 предыдущего адреса, второй вход — с выходом регистра 9, другой вход которого соединен с выходом блока

17 управления обменом.

Остальные связи между блоками устройства показаны на чертеже.

Минимальной единицей информации, адресуемой индивидуально, является слово длиной и двоичных разрядов. Физической ячейке модулей памяти 1 и 2 соответствует четыре различных адреса, отличающихся двумя младшими разрядами. Условимся, что коду

00 этих разрядов соответствуют разряды физических ячеек памяти, связанные с буферным регистром памяти 4, коду 01 — разряды, связанные с буферным регистром памяти 5 и т. д. Слово длиной 2п двоичных разрядов размещается в первой или второй половине физической ячейки памяти и его адрес, представленный в двоичном коде, оканчивается по крайней мере одним нулем. Слово длиной 4п двоичных разрядов занимает одну физическую ячейку памяти и имеет адрес, оканчивающийся по крайней мере двумя нулями. Указание

491952 длины слова, как правило, содержится в коде операции обращения к памяти и поступает в устройство оперативной памяти из процессора как при чтении, так и при записи. Исключение составляют операции чтения в тех случаях, когда процессор не может заранее указать длину запрашиваемого слова.

Номер модуля памяти, к которому производится обращение, указывается в соответствующем поле адреса.

Устройство работает следующим образом.

Для записи в память слова длиной и двоичных разрядов записываемое слово должно находиться в первом буферном регистре

12 процессора, а его адрес — в регистре адреса 8, В случае, если младший двоичный разряд адреса равен нулю, производится выдача записываеvîãо слова на выходы первого блока переключения 20 первой ступени коммутации 18, если равен единице — на выходы второго блока переключения 21 первой ступени коммутации 18; аналогично в соответствии со значением следующего двоичного разряда адреса записываемое слово поступает на чьтходьт одного из блоков переключения второй ступени коммутации 19 и принимается в гребуемый буферный регистр памяти 4, 5, 6 или 7, после чего происходит его запись в модуль памяти 1 или 2, при этом остальные три и-разрядных символа, хранящиеся в физической ячейке памяти, к которой произошло обращение, остаются без изменения, т. е. в этих частях ячейки производится чтение, и считанные символы принимаются в соответствующие буферные регистры памяти. Эти символы, как и вновь записанный символ, сохраняются в буфере памяти 3 до момента очередного запуска модуля памяти 1 или 2.

Запись в память двухсимвольных слов производится следующим образом. Записываемое слово помещается в первый и второй буферные регистры 12, 13 процессора и передается на выходы первой ступени коммутации

18 без изменения. Если второй младший двоичный разряд адреса равен нулю, записываемое слово передается посредство т первого и второго блоков переключения 22, 23 второй ступени коммутации 19 в первый и второй буферные регистры памяти 4, 5, если равен единице — посредством третьего и четвертого блоков переключения 24, 25 второй ступени коммутации 19 в третий и четвертый буферные регистры памяти 6, 7, после чего происходит его запись в модуль памяти 1 или 2.

Для записи в память слова максимальной длины записываемое слово помещается в буфер процессора 11, откуда без изменения передается в буфер памяти 3 с помощью блока коммутации 16.

Каждая запись в модуль памяти 1 или 2 сопровождается переписью адреса физической ячейки памяти, в которую производится запись, в регистр 9 предыдущего адреса.

Таким образом, в результате любой из описанных операций записи слово, переданное

65 из процессора, записывается в модуль памяти

1 или 2; кроме этого, адрес фнзи.еской я тейки памяти, в которую произведена запись, передается в регистр 9 предыдущего адреса, а содержимое этой ячейки уcT;!HBB.lèâàåòñÿ в буфер памяти 3.

Выполнение алгоритма обмена словом переменной длтшы обеспечивает блок 17 унрлвления обменом: необходимые перек,7та тстнтя 3 блоке коммутации 16, з-пуск модуля и,".мят:I

1 или 2, прием в буфер памяти 3 зяпнсывяемых символов с выходов блока камлтутлтттттт

16 и остальны.; снмво-.îâ с выходов,о.7i.,l7 памяти 1 нлп 2, перепись ". ресл фнзII I.ñêîll ячейки памяти в регистр 9 прсдьтдутцега адреса осуществляются под управ 7стнтем с,I,7,. ов, вырабатываемых этим 070Ko.,I. По оканчлттнн цикла обращения к памяти блок 17 упрлвления обменом посылает в "pc .тессар сигнал. указывающий, что возт тожтто с,7ед .таите е обращение к памяти.

Операции чтения из аператттвной памяти производятся путем обр",щетнтя к модулю памяти 1 или 2 только в случае, ес7II занроше Iное слово отсутствует в буфере памяти 3.

Поэтому любая операция пения начин".сТсН с анализа сигнала сравнения, выр,",б,".тывлсмого блоком срлвнснття 10. Гс."и сигнал свлвнения отсутствует, проттзводтттся обращение к модулю памяти 1 нли 2 по адрес .. уклзлнному в регистре адреса 8, после чего адрес опрашиваемой ячейки плмят т передлется в регистр 9 преды7ущего адреса. Через определенное время, неабходп»ое для приема считанного кода в буфер пытяттт 3, блок 17 управления обменом вырабатывает сиги".,7I.I управления блоком комт, тяцтттт 16, необходимые для передачи запрашенного слова нз буфера памяти 3 в буфер процессора 11. После завершения цикла обращения к хтадулю памяти 1 или 2 в процессор передается снгнлл, указывающий, что возможно следуютцее обращение к памяти.

Обращение к модулю памяти 1 нлн 2 не производится, если блок сравнения 10 вырабатывает сигнал сравнения. В этом случае блок 17 управления обменом сразу после приема кода операцитт чтения вырлблтывлет c»l.Haлы управления, обеспечнвгтащне переда ту запрошенного слова посредствам блока коммутации 16 из буфера памяти 3 в буфер процессора 11, а затем сигнализирует, что устройство готово к обмену слет.ющпм словам.

В случае, когда процессор указывает длину запрашиваемого слова, связь между буфером памяти 3 и буфером процессора 11 организуется следующим образом.

Слова максимальной длины перед".þòñë в буфер процессора 11 посредством блока коммутации 16 без изменения. Двухсттхтвальные слова передаются на входы III. 17I îãî II второго блоков переключеттня 20, 21 первой ступени коммутации 18 II3 первого н второго буферных регистров памяти 4, 5 посредством первого и второго блоков переключения 22, 491952

23 второй ступени коммутации 19, если второй младший двоичный разряд адреса равен нулю, и из третьего и четвертого буферных регистров памяти 6, 7 посредством третьего и четвертого блоков переключения 24, 25 второй ступени коммутации 19, если этот разряд равен единице. Первая ступень коммутации

18 передает двухсимвольное слово в первый и второй буферные регистры 12, 13 процессора без изменения. Выделение односимвольного слова в процессе его передачи в буфер процессора 11 происходит в два этапа: в соответствии со значением второго младшего двоичного разряда адреса первая либо вторая пара символов, хранящихся в буфере памяти

3, посредством второй ступени коммутации 19 передается на входы первой ступени коммутации 18, а затем в соответствии со значением младшего двоичного разряда адреса требуемый символ поступает в первый буферный регистр 12 процессора.

Чтение из оперативной памяти может также выполняться без указания длины запрашиваемого слова, например, при выборке команды (или микрокоманды). Пусть в вычислительной машине используются двухсимвольные, четырехсимвольные, шестисимвольные и восьмисимвольные команды, размещаемые в памяти следующим образом: двухсимвольная команда располагается в первой или второй половине физической ячейки памяти, четырехсимвольная занимает целую ячейку, шестисим вольная — одну ячейку и первую половину второй, восьмисимвольная — две физические ячейки памяти. Адрес команды указывает ее первый символ, являющийся кодом операции. Двоичная запись адреса двухсимвольной команды оканчивается по крайней мере одним нулем, любой другой команды — по крайней мере двумя нулями.

Выборка команды (микрокоманды) из оперативной памяти производится следующим образом. В соответствии с адресом, установленным в регистр адреса 8, производится считывание содержимого требуемой физической ячейки в буфер памяти 3. Поскольку в блок управления обменом не поступило указания длины запрашиваемого слова, исходной информацией для управления передачей из буфера памяти 3 в буфер процессора 11 является только адрес команды. Если адрес оканчивается двумя нулями, содержимое буфера памяти 3 без изменения передается в буфер процессора 11, если адрес оканчивается одппм Hóëåì, содержимое третьего и четвертого буферных регистров памяти 6 и 7 передается в первый и второй буферный регистры процессора 12 и 13 соответственно, в результате код операции всегда оказывается в первом буферном регистре процессора. Далее происходит передача содержимого буфера процессора в первую половину регистра команд (микрокоманд) устройства управления вычислительной машины, где происходит определение длины команды по коду операции.

Если команда двухсимвольная, третий и четвертый символы, переданные в регистр команд, не учитываются, и вычислительная машина приступает к выполнению команды.

Если команда четырехсимвольная, используются все четыре переданные символа. В случае шестисимвольной команды производится повторное обращение к устройству оперативной памяти, передача считанного кода из буфера процессора 11 во вторую половину регистра команд и начинается ее выполнение, причем два последних символа не учитываются. Аналогично происходит выборка восьмисимвольной команды.

Описанный алгоритм выборки слов без указания процессором их длины может использоваться в вычислительной машине также при чтении данных, представляемых, например, словами произвольной длины, при этом количество символов, используемых в слове, может указываться первым символом слова.

Формула изобретения

Устройство для обмена информацией между оперативной памятью и процессором, содержащее регистр адреса, блок управления обменом, подключенный к буферным регистрам памяти, буферные регистры процессора, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит блок сравнения, регистр предыдущего адреса и блок коммутации, входы и выходы которого подключены к соответствующим выходам и входам буферных регистров, а управляющие входы соединены с выходом блока управления обменом, к одному из входов которого подключен выход блока сравнения, первый вход которого соединен с выходом регистра адреса и одним из входов регистра предыдущего адреса, второй вход — с выходом регистра предыдущего адреса, другой вход которого соединен с выходом блока управления обменом.

491952

7á

19

8 !

Составитель В. Рудаков

Техред Е. Митрофанова

Редактор Б. Нанкина

Корректор А. Степанова

Типография, пр. Сапунова, 2

Заказ 113/10 Изд. Ма 1982 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 475