Ячейка памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

00 49I998

Со оз Советских

Социалистических

Республик

1

}

t (61) Зависимое от авт. свидетельства (22) Заявлено 28.05.74 (21) 2029053/18-24 (51) М. Кл. G 11с 11/40 с присоединением заявки №

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (32) Приоритет

Опубликовано 15.11.75. Бюллетень № 42

Дата опубликования описания 06.02.76 (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

И. А. Аракчеева, В. А. Иванов, В. В. Прушинский, А. С. Савлук, А. П. Удовик и А. Г. Филиппов

Московский ордена Трудового Красного Знамени инженерно-физический институт (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Предлагаемая ячейка памяти относится к области вычислительной техники и предназначена для использования в качестве запоминающего элемента в оперативных запоминающих устройствах цифровых вычислительных систем.

Известны ячейки памяти, содержащие два двухэмиттерных транзистора и — p — и-типа, два нагрузочных и два переключающих транзистора р — и — p-типа, в которых коллекторы первого двухэмиттерного, первого нагрузочного и второго переключающего транзисторов объединены и подключены к базам второго двухэмиттерного и первого переключающего транзисторов, коллекторы второго двухэмиттерного, второго нагрузочного и первого переключающего транзисторов объединены и подключены к базам первого двухэмиттерного и второго переключающего транзисторов, первые эмиттеры двухэмиттерных транзисторов подключены к соответствующим разрядным шинам, а вторые — к числовой шине.

Недостатком таких ячеек памяти является завышенная мощность, потребляемая запоминающим устройством в режиме выборки. Это объясняется тем, что при необходимости выбора из матрицы памяти одного двоичного разряда необходимо перевести в возбужденное состояние все ячейки слова (горизонтальный ряд ячеек), в котором находится искомый разряд. Это вызывает дополнительный расход энергии в режиме выборки и ведет к снижению быстродействия запохтипающего устройства.

Кроме того, быстродействие ячейки дополнительно снижается из-за большого перепада уровней напряжения числовой шины (имеющей значительную с»кость) при переключении слова из режима хранения в возбуждсн10 ное состояние.

Целью изобретения является повышение быстродействия ячейки памяти.

Указанная цель достигается подключением эмиттеров переключающих транзиторов к ба15 зам нагрузочных транзисторов и соединснием пх с шиной смещения.

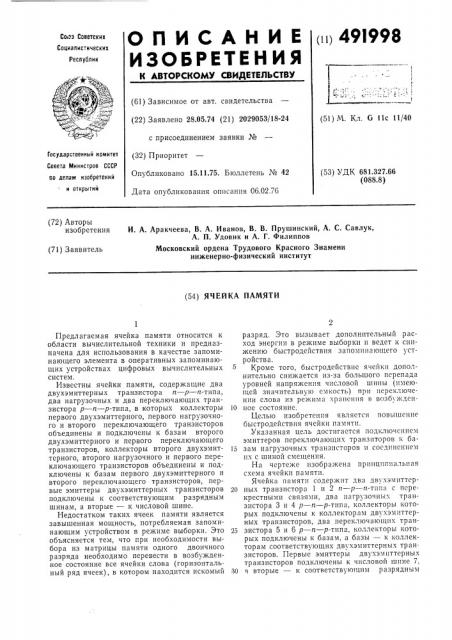

На чертеже изображена пршщппиальная схема ячейки памяти.

Ячейка памяти содержит два двухэмпттер20 ных транзистора 1 и 2 и — р — и-типа с псрекрестными связями, два нагрузочных транзистора 3 и 4 р — n — р-типа, коллекторы которых подключены к коллекторам двухэмиттерных транзисторов, два переключающих тран25 зистора 5 и 6 р — n — р-типа, коллекторы которых подключены к базам, а базы — к коллекторам соответствующих двухэмиттерных транзисторов. Первые эмиттеры двухэмиттерных транзисторов подключены к числовой шине 7, 30 а вторые — к соответствующим разрядным

O I3

60 шинам 8 и 9. Шина питания 10 объединяет эмиттеры нагрузочных транзисторов, а шина смещения 11 — базы нагрузочных и эмиттеры переключающих транзисторов. Усилитель записи-считывания 12 управляет работой ячейки с помощью разрядных шин.

Шина смещения 11 сосдинена через диод 13 с разрядной шиной 7, которая, в свою очередь, через токозадающий резистор 14 подключена к отрицательной шине 15 источника питания.

Ячейка памяти работает в трех режимах:

1) режим хранения информации;

2) режим считывания информации;

3) режим записи информации.

В режиме хранения информации к шине 10 приложен низкий уровень напряжения. Нагрузочные транзисторы р — и — р-типа 3 и 4 являются источниками тока хранения и поддерживают ячейку в одном из двух устойчивых состояний в этом режиме работы. Необходимый ток коллекторов транзисторов 3 и 4 задается базовым током этих транзисторов через диод 13 и резистор 14. 11ереключающие транзисторы р — n — р-типа 5 и 6 в этом режиме закрыты, так как закрыты эмиттеры двухэмиттерных транзисторов 1 и 2, подключенные к разрядным шинам 8 и 9, а падение напряжения на диоде 13 недостаточно для открывания переключающего транзистора, база которого подключена к коллектору насыщенного двухэмиттерного транзистор а.

Пусть перед считыванием информации двухэмиттерный транзистор 1 был насыщен.

В момент считывания потенциал на шине питания 10 увеличивается. Это ведет за собой увеличение потенциала на шине смещения 11, к которой подключены эмиттеры переключающих транзисторов 5 и 6. Транзистор 5 открывается, так как база его подключена к коллектору насыщенного транзистора 1, а эмиттер транзистора 1, подключенный к разряднои шине 8, после некоторого увеличения потенциала на шине питания 10 фиксируется достаточно низким уровнем входного напряжения усилителя записи-считывания 12. Эмиттерный ток насыщенного транзистора 1 резко увеличивается, что обеспечивает быстрое включение усилителя 12. При этом за счет коллекторного тока транзистора 5 обеспечивается увеличение тока базы транзистора 1, необходимое для поддержания его в насыщенном состоянии, так как коллекторного тока нагрузочного транзистора 4 в момент считывания информации для этого недостаточно.

Транзисторы 2 и 6 закрыты из-за недостаточного для открывания напряжения на переходах база — эмиттер. После считывания информации напряжение на шине питания 10 понижается, и ячейка возвращается в режим хранения информации, не изменив своего состояния.

В режиме записи информации на одной из разрядных шин, например на шине 9, с помощью усилителя записи-считывания 12 устанавливается низкий уровень потенциала. Тогда, после увеличения потснциала на шине питания 10, ток течет в базу двухэмиттерного транзистора 2, к эмиттеру которого приложен низкий уровень потенциала. Транзистор 2 открывается, и током коллектора этого транзистора закрывается транзистор 1, также открывается переключающий транзистор 6. Током коллектора переключающего транзистора

6 закрывается транзистор 5 и поддерживается в насыщении транзистор 2. Ячейка переключилась в другое состояние. После записи информации напряжение на шине 10 понижается, транзистор 6 закрывается, и ячейка возвращается в режим хранения информации, изменив свое состояние.

Ячейка памяти проста по конструкции, так как транзисторы 1 и 5, 2 и 6 попарно выполняются в одной и- области, а нагрузочные транзисторы 3 и 4 выполнены в общей и-области для целого слова матрицы памяти. Так как мощность, потребляемая ячейкой в режиме хранения информации, на несколько порядков ниже мощности, потребляемой в режимах записи-считывания, а частота обращения к данному кристаллу оперативного запоминающего устройства невысока, средняя мощность, потребляемая интегральным оперативным запоминающим устройством, изготовленным на основе предлагаемой транзисторной ячейки памяти, будет примерно равна мощности, потребляемой устройством в режиме хранения информации.

Экспериментальные исследования, проведенные на интегральных образцах описанной ячейки, полностью подтверждают выводы, изJIo?KeíHûå выше.

Формула изобретения

Ячейка памяти, содержащая первый и второй двухэмиттерные транзисторы и — р — n-типа, причем база первого соединена с коллектором второго, а база второго — с коллектором первого, первые эмиттеры обоих транзисторов подключены к соответствующим разрядным шинам, вторые — к числовой шине, к коллекторам первого и второго двухэмиттерных транзисторов подключены соответственно базы первого и второго переключающих и коллекторы первого и второго нагрузочных р — n — р-транзисторов, к базе каждого двухэмиттерного транзистора подключены коллекторы соответствующего переключающегс транзистора, а эмиттеры нагрузочных транзисторов подключены к шине питания, о тл ич а ю щ а я с я тем, что, с целью повышения быстродействия ячейки, в ней эмиттеры переключающих транзисторов подключены к базам нагрузочных и к шине смещения.

491998

77

Составитель В. Иванов

Техред Е. Митрофанова

Редактор Б. Нанкина

Корректор Т. Миронова

Типография, пр. Сапунова, 2

Заказ 94/15 Изд. ¹ 1973 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5