Преобразователь напряжения в частоту

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

iii 492036

Соаа Соитоких

Сокиалиотическнк

Рвоа блик

-Ф (61) Дополнительное к авт. свид-ву (22) Заявлено 17.04.73 (21) 1908359/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 15.11.75. Бюллетень № 42

Дата опуоликовянпя описания 01.04.76 (51) М. Кл. Н 03k 13/20

Государотвеииый комитет

Сое.та Ы;еаиотров СССР ио долам изобретений и открытий (53) УДК 681.325(088.8) (72) Авторы изобретения (71) Заявитель

Ю. М. Туз, О. П. Синицкий, В. И. Губарь и Е. T. Володарский

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалист:ческой революции (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЧАСТОТУ

Изобретение относится к измерительной технике и может быть использовано при построении точных измерительных преобразователей, я также цифровых вольтметров постоянного и переменного тока.

Известен преобразователь напряжения в частоту (ПНЧ), содержащий интегратор, выход которого подключен ко входу компаряторя, эталонный конденсатор, подключенный через первый ключ ко входу интегратора н через второй ключ ко входу источника эталонного ня пряжения.

Известный преобразователь имеет следующHp. недостатки: прн изменении фронтов импульсов, упра вляющих ключами, возможно паразитное прохождение тока на вход инте"pampa; изменение длительности импульса ждущего мульти1вибратора вызывает погрешность во всем рабочем диапазоне преобразователя; пз-за ограниченного времени разряда этало;шого конденсатора более жесткие требования предъявляются к элементам обратного преобразователя и особенно к ключам.

Для повышения точности и расширения динамического диапазона, в предлагаемый преобразователь введены дополнительный компаратор, триггеры, запускающая схема, схема

ИЛИ, схемы задержки и формирователь импульсов, через который выход дополнительного компаратора подключен непосредственно к нулевому входу первого триггера, управляющего первым ключом, и к единичному входу второго триггера через первую схему задержки, выход основного компаратора под5 ключвн к нулевому входу второго триггера и к запускающей схеме, а также через вторую схему задержки соединен с единичным входом первого триггера, выходы второго триггера и запускающей схемы соединены со входами

10 схемы «ИЛИ», управляющей вторым ключом.

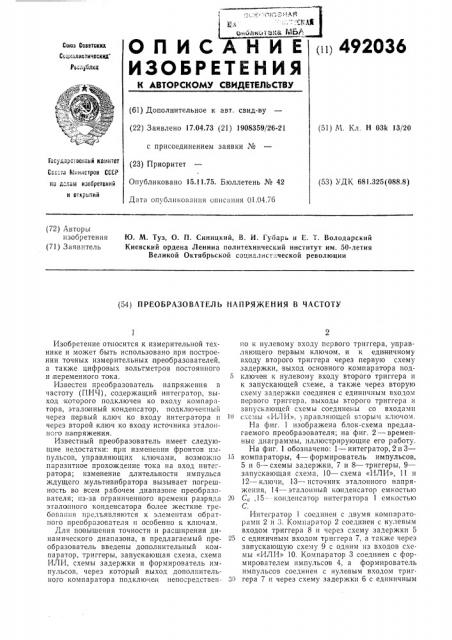

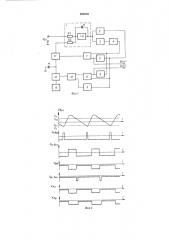

На фиг. 1 изображена блок-схема предлагаемого преобразователя; на фиг. 2 — временные диаграммы, иллюстрирующие его работу.

На фиг. 1 обозначено: 1 — интегратор, 2 и 3—

15 компараторы, 4 — формирователь импульсов, 5 и 6 — схемы задержки, 7 и 8 — триггеры, 9— запускающая схема, 10 — схема «ИЛИ», 11 н

12 —.ключи, 13 — источник эталонного напряжения, 14 — эталонный конденсатор емкостью

20 С„,15- конденсатор интегратора 1 емкостью

С.

Интегратор 1 соединен с двумя компараторами 2 и 3. Компяратор 2 соединен с нулевым входом триггера 8 и через схему задержки 5

25 с единичным входом триггера 7, а также через запускающую схему 9 с одним из входов схемы «ИЛИ» 10. Компаратор 3 соединен с формирователем тпмлульсов 4, а формирователь импульсов соединен с нулевым входом триг30 гера 7 и через схему задержки 6 с единичным

492036 входом триггера 8. Триггер 7 соединен с ключом 11, а триггер 8 через .схему «ИЛИ» с ключом 12. Источ ник эталонного напряжения

13 через ключ 12 соединен с эталонным конденсатором 14 емкость Со, а эталонный конденсатор 14 через ключ 11 соединен со входом интегратора 1. Входное напряжение через сопротивление поступает на интегратор 1, собранный на операционном усилителе, выход которого соединен с компараторами 2 и 3.

Когда напряжение на выходе интегратора достигает уровня срабатывания компаратора 2

U, (фиг. 2), то последний выдает на входы триггера 8 и схемы задержки 5 скачок напряжения. Сначала срабатывает триггер 8 и через схему «ИЛИ» 10 закрывает ключ 12, отключая при этом эталонный конденсатор 14 от источника эталонного напряжения 13 (Е,,). ь1ерез время задержки схемы задержки 5 срабатывает триггер 7 и открывает ключ 11.

Начинается разряд конденсатора 14 на вход интегратора 1, и конденсатор 15 емкостью С перезаряжается от U> до U4 (фиг. 2). При переходе напряжения на выходе и нтегратора

1 через уровень срабатьивания компаратора 3

U», последний выдает положительный скачок напряжения, но формирователь импульсо в 4, стоящий на выходе компаратора 3 не выдает импульса, так как он срабатывает только при перепаде ва его входе от плюса к минусу.

После окончания разряда конденсатора 14, конденсатор 15 начинает перезаряжаться от входного на пряжения от U4 до Uz. При переходе напряжений на выходе интегратора 1 через уровень срабатывания компаратора 3

U,2 последний выдаст отрицательный скачок напряжения и при этом формирователь импульсов 4 сформировывает импульс отрицательной полярности длительностью 1 — 3 мкс.

Этот импульс поступает на вход триггера

7 и через схему задержки 6 на вход триггера

8. Сначала срабатывает тригер 7 и закрывает ключ 11, отключая таким образом конденсатор 14 от входа интегратора 1. Через время задержки схемы 6 срабатывает триггер 8 и открывает ключ 12. Конденсатор 14 зарядится до напряжения Е„и его разряд происходит после достижения напряжением на выходе компаратора 2 уровня U„ . В дальнейшем работа происходит аналогично описанному. Таким образом, частота на выходе ПНЧ будет равна: где R — сопротивление резистора R2.

При включении ПНЧ может возникнуть такое состояние, что ключ 11 будет открыт, ключ

12 закрыт, а емкость С конденсатора 15 интегратора 1 заряжена, входным положительным напряжением. Если емкость Со конденсатора 14 при включении ПНЧ не успевает зарядиться от источника эталонного напряжения (Е,,), то на конденсатор 15 не поступает импульс обратной связи и устройство находится в таком состоянии до тех пор, пока U„, не становится равным нулю, а потом опять возрастает.

Для устранения этого недостатка служит запускающая схема 9, которая через схему

15 «ИЛИ» 10 открывает ключ 12 и перезаряжает конденсатор 15.

Таким образом, благодаря асинхро|нной ра боте триггеров 8 и 7 полностью исключается паразитное прохождение тока на вход инте20 гратора.

Поскольку время заряда емкости эталонного конденсатора 14 ра вно времени ее разряда при любой выходной частоте преобразователя, то значительно уменьшается попреш25 ность от нестабильности многих элементов обратного преобразователя.

Формула изобретения

Преобразователь напряжения в частоту, содержащий интегратор, выход которого под35 ключен ко входу компаратора, эталонный конденсатор, подключенный через первый ключ ко входу интегратора и через второй ключ ко входу источника эталонного напряжения, отличающийся тем, что, с целью повыше40 ния точности и расширения динамического диапазона, в него введены дополнительный компаратор, триггеры, запускающая схема, схема «ИЛИ», схемы задержки и формирователь импульсов, через который выход допол45 нительного компаратора подключен непосред ственно к нулевому входу первого триггера, управляющего первым ключом, и к единичному входу второго триггера через первую схему задержки, выход основного компарато50 ра подключен к нулевому входу второго три гера и к запускающей схеме, а также через вторую схему задержки соединен с единичным входом первого триггера, выходы второго триггера и запускающей схемы соединены со

55 входами схемы «ИЛИ», управляющей вторым ключом.