Многоканальный регистратор

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистических

Республик

<1» 492879 (61) Дополнительное к авт. свнд-ву (22) Заявлено15.01,73 (2I) 1880665/18-24 (51) М, Кл, б 06 ) 15/20 с присоединением заявки № (23) Приоритет (43) Опубликовано 25-11-75Бюллетень g». 4З (45) Дата опубликования описания

Гасударственный намнтет

Савата Инннстааа СССР аа делам нзобрепннй

II OTKPbifkiI (53) УДК

681,32 6. (088.8) (72) Автор. изобретения

В, fl. Зеленин (71) Заявитель

Пермский ордена Трудового Красного Знамени государственный университет им.А.М.Горького (54) МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР

Изобретение относится к вычислительной технике, в частности к устройствам

i для регистрации информации, и может быть использовано s спектроскопии магнитного резонанса. а

Известен многоканальный регистратор, содержащий регистр адреса, первая группа выходов которого соединена с адресными входами запомннаюшего блока, информационные выходы которого соединены с груп- р пой входов регистра числа, соединенного через аналого-цифровой преобразователь с входом многоканального регистратора, выход которого соединен с выходом блока формирования импульсов, счетчик, соеди- И пенный с первой группой входов схемы сраанения, блок управления, выходы которого соединены с входами регистра адреса, запоминающего блока и регистра числа, причем выходы регистров адреса и числа че- 20 реэ соответствующие цифро-аналоговые преобразователи соединены с индикационными выходами многоканального регистратора»

Однако отсутствие возможности однов- l Ж ременной регистрации II отображения ин формации, в особенности при низкой частоте повторения импульсов, снижает бысч родействие регистратора.

klem изобретения - повышение производительности устройства.

Достигается это тем, что многоканальный регистратор содержит реверсивный счетчик, дополнительную схему сравнения, блок формирования интервалов и блок программ причем соответствующий выход блока управления соединен с первыми входамн бло ка формирования интервалов н блока прог рамм, выходы которого соединены с sxoдом блока формирования импульсов, со вторым входом блока формирования интервалов, с соответствующим входом аналога-цифрового преобразователя, первым входом блока управления и входом реверсивного счетчика, первая группа выходов которого и вторая группа выходов perII ра адреса соединены с группами входов дополнительной схемы сравнения, выход которой соединен со вторым входом блока управления второй вход блока программ 1}з> 87Г) соед««нен с выходом схемы сравнения, Вторая группа входов которой соединена со второй группой выходов реверсивного счетчика, а выход блока формирования интервалов соединен со входом счетчика.

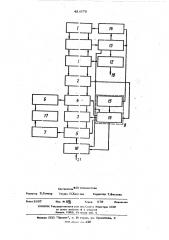

На чертеже - блок-схема многоканального регистратора.

Многоканальный регистратор содержит схемы сраинения 1 и 2, запоминающий блок 3, регистр адреса 4, регистр числа 5, цифро-анялоговьее преобразователи Ь, 7„ блок управления 8, реиерсивный счет чик 8, аналого-цифровой преобразователь 0 счетчик 11, блок 12 формирования импулесов, блок программ 13, блок 14 формиро« вания интериалов„

Кроме гого на чертеже обозначены Генератор 15 тактовых частот, узел 16 управления, устройство 17 индикации, вход 18 и выход 19 многоканального регистратора, Регистратор р;)6îò«åò следующим Об разом. В рогистраторе реях!Изуется режим непрерывного наблюдения информации, хряняшейся B запоминающем блоке 3.

При этом по сигналам из блока управления 8 регистр адреса 4 выбирает цоследовательно ячейки заломи»}цошего блока 3, содержимое которых выводится ця регистр числя 5. Коды из регистра адреса 4 и регистра числа 5, преобразованные и яцалоговые величины цифро-аналоговыми IipeОбразовятелями 0 Ни 77, поступают»а устройство индикации 17, ца экране которого наблюдается график зарегистрированной фуе«кции. Период опроса всех ячеек залом и и ак) щего блока 3 — Т М, где 1, «время сбрш!«ения к одной ячейке запоминающего. блока 3, а }ее - число ячеек запоминающего блока 3.

Период Т задается генератором тактовых частот 15, блока управления 8.

На выходе 19 многоканального регис1ратора иырабатьеиается серия имиульсои с периодом повторе}«е!я Т и A Т периода опроса всех ячеек QQIIGM»f«Qior)rei-o блока 3.

Иыпол}«ение этого условия необходимо для того, чтобы обеспечить регистрацию сигнала, возбужденного предшествующей серией импульсов, в любой ячейке запоминающего блока 3 за Бремя генерации последующей серии импульсов.

По пусковому импульсу, поступающему иэ гонератора 15 тактовых частот, блок программ 13 посылает кома««ду и блок 12 формирования импульсои на формирование первого импульса серии и в блок 14 формирования интервалов цв формирование первого интервала между импульсами. Ьлци, .ф форми зовяц!!Е} ие!тереза}!ОБ мОж(}Y Бе !()обяTbIBQть неског!ько !1!!Тере)йлои >})икси}зовяццой длительцоа-.ги. Пусть первый интервал имеет фе«ксироианцую длителье«ость. Тогда

Ц блок L4 формирования интервалов BbfpQбать«Бает Один из фиксировяе«нь«х ие«териалОБ> и сиГцял Конец HfITBPBQJiQ постУпает В блок программ 1 3, KGTGpblA BbrpQ6QTb«BQет ко)>«янг«ы ня формирование второго импульсе! и второго интервала. Допустим, что следующий интервал имеет перемеи»ую длиTeJIb»GGть. »Тот интервал формируется пуТЕМ МЦОГОКРЯТНОГО Е!ОБТОЕ)0ЦИЯ GJ4} ОГО ИЭ фиксироияеп«ых интервялои. И этом слу«ае )>! си !.1«ялы К О! Iец и цте езв>ала lii 1 611ок а 1 >е форм и}> Оиян и я ие«тервалои ПОсту 1!ЯIОт В счет чик 3 1 ДО .Г ..х nop. HGKQ код B счет>«ике 1 1

11е 6 )>14е 1 е)явен код) > зяГ}исан}«О>>«у Б р!.Бе р сии»ом счетчике 9, и ня выходе схемы

g сравнения 1 це появится сигнал, который поступит Б блок программ 13, 11Я этом формировя}ц«е Беременно«.о интервала закан «и)з!)ется. Ьлок программ 13 цри этом

Вырабатывает комяцдь« ця формирование

@ о>«еред}!ОГО е«мпу«!ьса и интервала серии. После отработки последнего интерв«ла ссрии

Е, ЭТОТ }>«Ol>>«>1}1 С ООТБЕY«:T)Ó e Т HG>}БЛ()»И }G 1!G-» лез!«ОГО с»Гнала»Я вхОде 18 м»ОГОк«цальНОГО Оегистрото зя1 с ВыхОдя блОкя це)01 4» (зо }. м 1 3 B )f }IQJIGIG-пи<а)>зоной f) pe G6) f»Q!) 01«A" тель 1С«поступает кома»д;} I«Q преобр«зовяiil»e BYОД»G1"O СИГi«QJIQ Б цифровой КОД; Я В блок - правления 8 =1«Q рязре )e!)!Ie цр«ц}мя сиг}«аля со схемы сравнения 2, 33 KpGM0 того с»ГИЯл с Вь«хода блока п«зогр!}}!и 13 поступает на Вход реверсииНОГО сче Гчико 8 и код, зяпе«сапный В счетчике 8, увеличивается .или умеш,шяется IIQ ед}«н«е!«у, обуслаил;«Боя тем самым измеце}О»ие задержки между им!Еульсами (перемее«цые 1!Итерияль!) при Генерации следующей серии. «е!«ерация следующей серии начинается с приходом очередного пускового импульса с генератора 15 тактовых частот

4) блока управления 8, и, практически, может начаться сразу же после выдачи команды с 131>«хода блока HpогpQMM 1 3} посколе>ку B соответствии с ус11оиием Т и Т, Бсе ячейки запоминающего блока 3 будут onИ рошее!и и входной сиг}«ал, полученный и предыдущей серии имцульсои, будет зярегисl рировяц прежде, чем появится очередной командный импульс на выходе блока ирогр 13.

Се!гнал ца выходе схемы срявце}«е«е« 2

ЦОЯВЛЯЕТСИ В МО}!ЕНТ, КОГДЯ !ЕО«4 Б РЕГИСТре адреса 4 равен коду и реверсивном счетчике &, т.е. длительность пе>реме»1«ьех и«етериалов серии приведе»я в сооти! тстиие

® с номером ячейки зацомицякпцего блока 3.

482879 и > О б р е; е н H Q! 3> О е- д м е

Й НОГО!ОН!альцый реГНСYpATDp, сОдержа

Ш3»A. Р»03 33СТ" > с3Д(30С0> П!»РВНЯ ГP3/Г!ПЗ ВЫХОДОВ

"» О о О О) О c . >(> д» ! >»> и а с ад р» с ц 3> M и в»ходам li запом33цз;Ои е>»-О блокr, ННФОрмапнонцые Выходы которого соединены с группой входов пегистра числа., соединенного через ацало>1.. .,!фрозой преобразователь с входом л3цс гоканальцoi-о регистратора, вь3ход которого с;.Опццан с выходом блока формирования

>! -!!".с 3-3 с-,ет-33!к с-о»ахц!!а!3!!ЫР с первой

» и! Нлг с н.>!ХО!»! Схемы сравнен»йя посъу» н;,е-!,з., унравлеиня Хб блока управлеf>»».Я >;.,.",". т едцн и в ырабатьп, азт коман ..» г» !! -„-:Га Н3не;; .! д, -: О- f> нз а3!ацог:;."-.-Дцфрового Н Р>!ИРО»»3ЯН "B С

3 в дa>!.3ой я..айке запомни а>оше,-о блока

> акц3:! сб зазол!» Об&"печ>Звуке» тся раоота

МБОГоканальнОГО ре> истратора при иепре ры;-ном на»бл3одении эа ходом эксперимента для с>!у iQrI ннзкОЙ частоты повтОренйя се

»33: и >»3 -г/Гь -Оа .»>3-О позволяет увеличить быстродействие регистратора»

>4

Йредлага»- >!ь. й» мцогокаивльц> !>! регяст-- . з ":. >: . раТОр >3!Ож i;" !iñ,. .i 1; !. Оц; «»цен»ц > для управ, уяц!!н > л» п»!Льсн 3л3-" > дер33ьи" i>»и» цнтць3м ра

HQHBèooi»i ЯМР - релаксо!Аетром нли дру;;. Од експериментальцой установкОй, группой входов схемь> сравнения, блок управления выходы кОтОрОГО сОединены с входами регистра адреса, зацоминак3!него блока и регистра числа, причем выходы

@ регистров адреса и числа через соответствук3шие дифро-аналоговые преобразователи соединены с индиканионнь!ми выходами регистратора, о т л и ч а к3 ш и и с я тем,. что, с делыо повышения производительности устройства, ой содержит реверсивный счеч чик, дополнительную схему сравнения, блок формирования иц.гервалов н блок программ, причем соответствукнццй выход блока управления соединен с 13ерв!!м3! входами бло ка формирования нцтервалое и блока про рамм выхОди кОтОрОГО соединены с вхо» дом блока фсрлирования импульсов, со вторым входом блока формирования нн первалсе„ с соответствукццим входом аналого-цифрового преобразователя, церн!>!л3 входом блока управления и входом реп р».явного счетчика, первая группа 333!кодо!3 которого и вторая группа выходов регистра щцн са соедииены с группами входов доиолннтельной я схемы сравнения, вь!ход которс и соединен со вторым входом блок 3 уира!3пення, второй вход бчока прогрнмм с!. единеH с выходом схемы сравнения, Beeps» группа входов которой соединена со ОтороФ группой выхоЩ дов ° реверсивного счетчика, а в3>!ход блока формирования интери3лон со пин! ц с входом счетчика.

Иэд. М t $) Ти рант 679

Подннсное

Эа«аз 2607

0НИИПИ Государственного «ом) тета Совета Мяннстрон СССР

I)0 делан нзобрете) )й и открытий

Москва, !)3035, Ра чмокая наб., 4 фнщнатт ППЦ Патент, г. У> горол, ул. Проектная, 4

П))П,Патент Зэк. 4«Г)) ф.Ш (гиахметова

Составнтедв

Редактор ЕХончар Телред Н.Хант ева Корректор .Т.Фисенно