Дешифратор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 493022

\

4

t

% (61) Дополнительное к авт. свид-ву (22) Заявлено 18.05.72 (21) 1785882/18-24 с присоединением заявки № (51) M. Кл.

Н 031 1 3/24 .

Государственный комитет

Сааета Министров СССР по делам изооретений и открытий (23) Приоритет (43) Опубликовано 25.11.75,Бюллетень № 43 (53) УДК 681.3 (088.8). (45) Дата опубликования описания 24.02.73 (72) Авторы изобретения

Л. В. Максимов и В. Л. Максимов (7 I) Заявитель (54) ДЕШИФРАТОР

Изобретение относится к области автоматики и вычислительной техники и может .быть использовано, в частности, при построении схем управления цифровых вычислительных машин. б

Известен дешифратор, содержащий диоды, первые два иэ которых анодами соединены с первой входной шиной дешифратора, а третий и четвертый — со второй входной шиной деши рратора, причем катоды первого и - )О третьего из них соединены соответственно с катодами пятого и шестого диодов, а через первый и второй резисторы — с первой шиной питания, катоды второго и четвертого диодов объединены и соединены с 15 катодом седьмого диода, а через третий резистор также с первой шиной питания, соединенной с первым выводом четвертого резистора, и нагрузочные резисторы, первые выводы которых связаны со второй ши- 20 ной питания.

Иедостатком извести от о дешифратора является сложность схемы.

Для упрощения схемы дешифратора в предлагаемом устройстве третья входная 25 шина соединена со вторым выводом четвертого резистора и с анодами дополнительных восьмого, девятого и десятого диодов, катоды которых соединены соответственно с анодами пятого, шестого и седьмого диодов, причем аноды пятого, шестого и седьмого диодов и второй вывод четвертого резистора соединены соответственно с первыми выводами конденсаторов, вторые выводы которых подключены соответственно к выходным шинам дешифратора и вторым выводам нагрузочных резисторов.

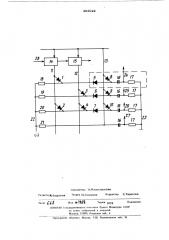

На чертеже приведеча схема депп1фрятора. Он состоит из диодов 1-)0, первой входной шины 11, второй входной шинь! (2, третьей входной шины 13 и второго вход» соответственно первого 14 и второго ) 5 разрядов счетчика, конденсаторов ) 6, -1грузочных резисторов 17, соответственно первого, второго, третьего и четвертого резисторов 18, ) 9, 20 и 21, первой шины питания 22, второй. шины питания 23, соответственно первого, второго, третьего и четвертого выходов 24, 25, 26 и 27 и первого выхода 28 разрядов счетчика.

493022

Первая входная шина 11 дешифратора соединена с анодами первого и второго дрло:> дов, катоды которых подключены соответственно через резисторы 18 и 20 к первой шине питания и к катодам диодов 5 и 7, аноды которых связаны соответственно с катодами диодов 8 и 10. Аноды диодов 8 и 10 соединены с третьей входной шиной 13, а катоды с соответствующими конденсаторами, вторые обкладки которых щ соответственно являются первым (24) и вторым (26) выходами дешифратора и через нагрузочные резисторы 17 подключены к второй шине питания 23.

Вторая входная шина 12 дешифратора 15 соединена с анодами диодов 3 и 4, катоды которых подключены соответственно через резисторы 18 и 19 к первой шине питания. Причем катод диода 3 соединен также с катодом диода 6, анод которого 20 связан с катодом диода 9, а через конденсатор 16 и нагрузочный резистор 17к второй шине питания 23. При этом в этой цепи анод диода 9 соединен с третьей входной шиной 13, а общая точка кон- 25 денсатора 16 и нагруэочного резистора

17 — с вторым выходом 25 дешифратора.

Четвертый выход 27 дешифратора под— ключен к общей точке того конденсатора

16 и нагрузочного резистора 17, связан- 30 ного с второй шиной питания 23, вторая обкладка которого через резистор 2 1 связана с первой шиной питания.

Первый вход 28 разрядов счетчика соединен с первым разрядом 14 счетчика, 35 а второй вход — с вторыми входами первого и второго разрядов счетчика.

Устройство работает следующим образом. Очередной импульс синхронизации по шине 13 приводит схему дешифратора в 40 исходное состояние, при котором первый и второй разряды счетчика очищены, диоды 1, 2, 3 и 4 дешифратора открыты, конденсаторы 16 разряжены, а диоды 5, .6 и 7 закрыты отрицательным потенциа- 45 лом шины 13.

При поступлении импульсов на вход де»

, шифратора счетчик пересчитывает их, образуя коды последовательного ряда чисел, которые используются в управлении рабо- 50 той дешифратора.

Образование очередного кода в счетчике вызывает появление сигналов на выходах дешифратора. В зависимости от структуры кода сигналы могут появиться как 55 на одном, так и на нескольких выходах, что обусловлено использованием только одного входа дешифратора на один разряд счетчика. Например, в разрядах счетчика фиксирован код числа "01". I 50

Согласно включенным диодам сигнал в

I виде отрицательного импульса появится ..только на втором выходе дешифратора.

Конденсатор 16 второго выхода дешифратора, заряжаясь через диод 6, сформирует отрицательный выходной импульс дешифратора. Код следующего числа "1 1" согласно включенным диодам дешифратора должен был бы вызвать появление сигнала на первом, втором и третьем выходе дешифратора. Однако выходной импульс

: возникнет только на третьем выходе. Сигналы, возникающие при этом на первом и втором выходе дешифратора в данном случае являются сигналами неоднозначности и подавляются диодами 5 и 6, заряженными в предыдущих тактах работы через конденсаторы 16 первого и второго выходов дешифратора.

Заряды конденсаторов удерживаются до очередного импульса синхронизации по ши» не 13, который должен привести схему дешифратора в исходное состояние. Затем цикл работы дешифратора повторяется.

Формула изобретения

Дешифратор, содержащий диоды, первые два из которых анодами соединены с первой входной шиной дешифратора, s трети и четвертый - со второй входной шиной дешифратора, причем катоды первого и третьего из них соединены соответственно с катодами пятого и шестого диодов, а через первый и второй резисторы — с первой шиной питания, катоды второго и четвертого диодов объединены и соединены с катодом седьмого диода, а через третий резистор — также с первой шиной питания, соединенной с первым выводом четвертого резистора, и нагрузочные резисто-; ры, первые выводы которых связаны со второй шиной питания, о т л и ч а ю щ и йс я тем, что, с целью упрощения дешифратора, его третья входная шина соединена со вторым выводом четвертого резистора и с анодами дополнительных восьмого, девятого и десятого диодов, катоды которых соединены соответственно с анодами пятого, шестого и седьмого диодов, причем аноды пятого, шестого и седьмого диодов и второй вывод четвертого резистора соединены соответственно с первыми выводами конденсаторов, вторые выводы которых подключены соответственно к выходным шинам дешифратора и вторым выводам нагрузочных резисторов. !

493022

Составитель Н.Милославская

Техред M.Cåìåíîâ Корректор З.Тарасова

Редакторя, Андреева

11((ИИ((И (осударственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 1!3035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская иаб„24

Заказ Изд. а ЩЯ Тираж 902 Подписное