Многофазный двоичный делитель

Иллюстрации

Показать всеРеферат

О П И C А Н И Е () 49зоз2

ИЗОБРЕТЕИИЯ

Союз Советских

Социалистических

Республик ф 1 * ), Я-" ф . 3p .Ъф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено22.11.71 (21)1716763/26-21 (51) р1 Кл H 03k. 23/02 с присоединением заявки _#_ (23) ПриоритеоГасударственный номнтет

Совета Мнннстров СССР по делам нзобретеннй н открытнй (43) Опубликоваио25.11.75 Бюллетень Хе 43 (53) УДК 621.374.22 (088.8) (45) Дата опубликования описания 13.04.76 (72) Автор изобретения

А. Н, Ф Ойд& (71) Заявитель (54) МНОГОФАЗНЫЙ ДВОИЧНЫИ ДЕЛИТЕЛЬ

1 ,- . Изобретение относится к области вычислительной и импульсной техники и может быть использовано для построения двоичных делителей частоты с многофазными. выходами а также для построения циклиФ

5 ческих счетчиков и распределительных устройств.

Известны многофазные двоичные делители, соцержашие распределитель сигналов на 2Ф-1 каналов и моностабнльные триг10 геры, каждый из которых выполнен из

2тт+ 1 алементов И-НЕ, соединенных в виде кольца, причем выход каждого элемента И-НЕ многостабильного триггера подс соединен к входу предыдущего и последуюшего элементов И-НЕ этого многостабильного триггера.

Цель изобретения - упростить схему многофазного двоичного делителя.

Это достигается тем, что вход одного

2 из элементов И-НЕ первого многостабильного триггера подсоединен к выходу первого канала распределителя, все следующие за ннм 2п элементов И-НЕ соединены с (выходами соответствующих 2п каналов

2 распределителя, один из входов первого элемента И-НЕ последуюшего многостабильного триггера соединен с выходом первого алемента И-НЕ предыдушего многостабильного триггера, вход второго алемента И-НЕ соединен с выходом третье, го элемента .1-НЕ,вход третьего элемента И-НЕ соединен с выходами пятого и т.д. до послед ° него нечетного элемента И-НЕ, а входы остальных элементов И-НЕ многостабильно го триггера соединены с выходамн четных элементов И-HE предыдушего многостабиль ного триггера, начиная со второго элемента И-НЕ.

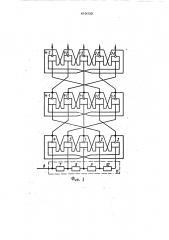

На фиг. 1 дана схема трехразрядного пятифазного двоичного делителя, на фиг.

2 — временная диаграмма его работы.

Двоичный делит.ль выполнен на логических элементах И-НЕ для положительных сигналов.

Каждый разряд состоит из пяти элемен- тов,"1,2,3,4,5; 1-1, 2-1, 3-1, 4-1, 5-1;

1-2, 2-2, 3-2, 4-2, 5-2, Выход каждого алемента каждого раэ-! ряда делителя подсоединен к входам IlpG

493ОЭ2 (лов, который вызывает появление на вылоде элемента 5 положительного потенциала.

Положительный потенциал с выхода элемента 5 поступает на вход элемента 4 и вызывает появление на выходе элемента 4 отрицательного потенциала.

В момент появляется отрицатель4 ный импульс на выходе 8 распределителя сигналов (на фиг. 2 указаны эпюры на выходах всех элементов схемы, причем эпюра номера соответствует эпюре напряжений на выходе соответствующего . элемента). Импульс на входе элемента 1 в момент 3 не изменит состояние его

4 выхода. l

В момент E появляется отрицатель5 ный импульс на выходе 9 распределителя сигналов, который поступает на вход элемента 2 и вызывает на выходе элемента 2 положительный потенциал. Положите-, льный потенциал с выхода элемента 2 поступает на вход элемента 1 и на выходе элемента 1 появляется отрицательный потенциал, так как на остальных входах элемента 1 положительный потенциал.

В момент 3 на выходе 10 появляе1

6 сН импульс. Данный импульс изменения состояния схемы не вызывает, так как на ! выходе элемента 3, на который он посту- пает, был уже положительный потенциал.

В момент 1 на выходе распределите7 ля 11 сигналов появляется второй импульс и, следовательно, на выходе элемента 4 поA явится положительный потенциад, который поступит на вход элемента 3-1 и Ъь зоI вет изменение его выходного потенциала на отрицательный, так как на остальных входах элемента 3 положительные потенциалы.

В момент на выходе 7 распреде8 лителя сигналов появляется импульс. Он не вызывает изменения состояния схемы.

В момент t на выходе 8 распредели-, 9 теля сигналов появляется очередйой отри» цательный импульс, который поступит на вход элемента 1 и вызовет на выходе элемента 1 положительный потенциал.

Положительный потенциал с выхода,элемента 1, поступая на вход элемента 5, вызывает изменение потенциала на выходе элемента 5 на отрицательный. В момент на выходе 9 распределителя сиг-. ° налов появляется импульс, Данный импульс не изменит состояния схемы. мы делителя.

В момент i появляется отрицательной (импульс на выходе 7 распределителя сигнабО

В момент 1 на выходе 10 распре11

) делителя сигналов появляется отрицатель1дыдущего и последующего элементов дан ного разряда, Так, выход элемента 1 первого разряда подсоединен ко входу предыдущего элемента 5 и ко входу последующего элемента 2, Аналогично выход эле- 5 мента 2 подсоединен ко входам элементов

1 и 3 и т.д, Вход элемента 4 первого мнэгостабильного триггера соединен с выходом 6 первого канала распределителя, Все следующие lo за ним 2й элементов многостабильного. триггера соединены со следующими соо Ъ ветствующими выходами распределителя, так элемент 7 соединен с выходом распределиj теля, а вход элемента 1 с выходом распре-5 делителя и т.д.

Один из входов первого элемента 1-1

И-HE последующего многостабильного триггера соединен с выходом элемента 1 предыдущего многостабильиого триггера, вход 20 элемента 2-1 соединен с выходом элемента 3, вход элемента 3-1 соединен с выходом элемента 5 и т.д. до последнего нечетного элемента И-НЕ предыдущего много стабильного триггера. Входы остальных элементов -H E многостабильного триггера соедине, ны с выходами четных элементов предыдущего многостабильного триггера, начиная со второго элемента.. Так,вход элемента 4-1 соединен с выходом элемента 2,а вход элемента 5-1 0 соединен с выходом элемента 4.

Все следующие разряды делителя под соединяются к предыдущему аналогично как второй разряд к первому.

Положительным качеством схемы также является то, что входные тактирующие импульсы для перного разряда делителя можно получить, применяя линию задержки. Причем выходные импульсы, управляющие первым раз-! рядом делителя могут иметь перекрытие.

Единственным условием является то, чтобы в любой момент времени в разряде делителя были два, а в следующий момент три рядом стоящие элемента, соединенные

j трнггерными связками,на которые в данный момент времени не поданы входные импульсы.

Предположим, что в первоначальный момент времени (см. фиг. 2) все раз-

1 ряды делителя находятся в положении с.низ- р ким потенциалом напряжения на выходе элементов 2 и 5 каждог-.: разряда и с высо» кими на выходе остальных элементов. В момент f на выходе 6 распределителя

55 сигналов появится отрицательный импульс.

Он не вызывает изменение состояния схежзО32 ный импульс, который вызывает на выхо-1 де элемента 3 положительный потенциал.

Положительный потенциал с выхода элемента 3 поступает на вход элемента 2 и вызывает на его выходе отрицательный 5 потенциал, так как на остапьных входах. элемента 2 действуют положительные потенциалы.

В момент 1. на выходе 6 распреде12 литепя появляется отрицательный импульс. 10

Этот импульс не вызывает никаких изменений состояния схемы.

B момент t на выходе 7 распредеl3 лителя появляется очередной отрицательны 1 импульс, который поступает на вход элемен-1 ,та 5 и вызывает его переключение и т. д, Аналогично будут переключаться элементы первого разряда при приходе следующих импульсов на вход первого разряда делителя, 20

На вход второго разряда делителя поступают импульсы с выходов элементов первого разряда.

На вход третьего разряда делителя поступают импульсы с выходов элементов 25 второго разряда делителя.

Работа второго и третьего разрядов делителя аналогична работе первого разряда, С выходов элементов первого разряда снимаются импульсы с периодом в два раза больше, чем период импульсов на входе делителя. С выходов элементов второго и третьего разрядов делителя снимаются им-. пульсы с периодом соответственно в четыре и в восемь раз больше, чем период импульсов на входе 6 делителя.

Скважность импульсов на выходе многовыходового двоичного делителя при малом

6

1 числе разрядов можно р гулировать с помощью линий задержек.

С ростом числа разрядов скважность импульсов на выходе делителя стремится ел.чин. Л 2т, я-1 где t5 - -количество элементов в разряде.

Формула изобретения

Многофазный двоичный делитель, содер- . жащий распределитель сигналов íà 2й

2 -+-1 каналов и многостабильные триггеры, каждый иэ которых выполнен иэ 25+ 1 элементов И-НЕ, соединенных в виде кольца, при1чем выход каждого элемента И-НЕ мно цстабильного триггера подсоединен к входу предыдущего и последующего элементов

И-НЕ этого многостабильного триггера, отличающийся тем,что,с целью упрощения схемы, вход одного иэ элементов И-НЕ первого многостабильного триггера подсоединен х выходу первого канала распределителя, все следующие эа ним 2fl элементов И-НЕ соединены с выходачи соответствующих 2 В каналов распре- ° делителя, один иэ входов первого элемента

И-НЕ последуюшего многостабильного триггера соединен с выходом первого элемента

И-НЕ предыдушего многостабильного тригl гера, вход второго элемента И-НЕ соеди- I нен с выходом третьего элемента И-НЕ, вход третьего элемента И-КЕ соединен с выходом пятого и т.д. до последнего нечетного элемента И- lE, а входы остал ных элементов И-НЕ многостабильного триг гера соединены с выходами четных элементов И-НЕ предыдущего многостабнльного триггера, начиная со .второго элемента, И-НЕ.

493032

4юе 2

Заказ 2592 филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Тираж Q Я Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам. изобретений. и открытий

Москва, 113035, Раушскаи наб., 4