Устройство для асинхронной пространственной коммутации

Иллюстрации

Показать всеРеферат

Bee;:: — ».

j» л»р»»»

ОЛ ИС "И"Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (1ц 493озт

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02.04.74(21) 2013285/26 9 с присоединением заявки №вЂ” (51) М. Кл.

Н 04 ) 3/00

Гасударственный комитет

Совета Министров СССР оо делам нзооретеннй н открытий (23) Приоритет (43) Опубликовано 25.11.75.Бюллетеиь № 43 (45) Дата опубликования описания О5 О2 76 (53) УДК 621.3е5.34 (088.8) (72) Автор изобретения

В. П. Чуркин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АСИНХРОННОЙ ПРОСТРАНСТВЕННОЙ

КОММУТАЦИИ

Изобретение относится к технике связй и может использоваться в коммутационных система х.

Известно устройство для асинхронной пространственной коммутации, содержащее вход- 5 ные регистры, входы которых соединены с соответствующими входящими адресно-инфор-, мационными магистралями, выходные реги-( стры, выходы которых соединены с соответствующими исходящими адресно-инфпрмаци- 10 онными магистралями, распределитель тактов, выходы которого подключены к управляющим входам соответствующих входных регистров, первый дешифратор и блоки памяти. 1Ü

Однако известное устройство обладает недостаточной пропускной способностью.

Целью изобретения является повышение пропускной способности устройства. для этого в устройстве выходы всех входФЕ ных регистров объединены и подключены к входу дешифратора и к входам блоков памяти, выходы которых соединены с входами соответствующих выходных регистров, при-, чем выходы дешифратора соединены с управ- ляющими входами соответствующих блоков памяти.

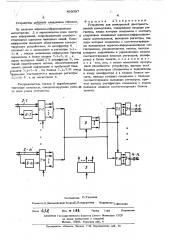

На чертеже приведена структурная элек трическая схема устройства.

Устройство дляасинхронной простран — ственной коммутации содержит входные регистры 1-1-1-Рт, входы которых соединены с соответствующими входящими адресноинформационными магистралями 2-1-2- т1. выходные регистры 3 1 3 ц, выходы которых соединены с соответствующими исходяшими адресно-информационными магистралями 4-1-4 ° распределитель тактов 5, выходы которого подключены к управляющим входам соответствующих входных регистров

1.-1-1- И, дешифраторы 6-1-6- т1 и блоки памяти 7 -1-7- tl причем выходы всех входных регистров 1 1-1- 1т, объединены и подключены к входу дешифратора 8 и к входам блоков памяти 7-1-7- Ь, выходы которых соединены с входами с ютветствуюших выходных регистров 3-1-3- tt, а выходы дешифратора 8 соединены с управляющими входами соответствующих блоков памяти 7, с

493О37

Составителв О,Тиконов редактор А.Зиньковский ТехредЕ.Подурушина Корректор

Т.фисенко

3а к аз ф Щ

Изд. ж I)gg Тираж 74Q Подписное

БНИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24

Устройство работает следующим образом, По входным адресно-информационным магистралям 2 в параллельном коде посту пает информация, сопровождаемая соответ-, ствующими адресами выходных линий. Если ° информация подлежит обслуживанию комму-I тируюшим устройством, то дешифратор 6 опознает ее и записывает в регистры 1-11-, откуда записанная информация будет1О переписана в блоки памяти 7-1-7- Я,, а адрес выходных линий — в дешифратор 8, кс . торый вырабатывает сигнал, обеспечивающий запись данной информации в требуемый блок:

l памяти 7-1-7- tl . Из блоков 7-1-7- fl ин 15 формация считывается в выходные регистры

3- 1-3- t1 и на магистрали 4.

Распределитель тактов 5 вырабатывает тактовые импульсы, синхронизируюшие рабо- 20 ту всех узлов устройства.

Ф ормула изобретения

Устройство для асинхронной пространственной коммутации, содержащее входные ре-. гистры, входы которых соединены с coma

t ствуюшими входящими адресно-информационными магистралями, выходные регистры, вью ходы которых соединены с соответствуюшими исходящими адресно-информационными магистралями, распределитель тактов, выходы которого под1ключены к управляющим входам, соответствующих входных регистров, дешифратор и блоки памяти, о т л и ч а ю ш е— е с я тем,,что, с целью повышения пропускной способности устройства, выходы всех входных регистров объединены ia подключены к входу дешифратора и к входам блоков памяти, выходы которых соединены с входами соответствующих выходных регистров, причем выходы дешифратора соединены с. управляющими входами соответствующих блоков памяти.