Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

"И йИЗОБРЕТЕН ИЯ

Союз Соввтскик

Социалистических

Республин (11) 4931 62

К АВТОРСКОМУ СВИДЕТЙЛЬСУВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 22 11,71 (2l) 1715908/18 24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.08.77.Бюллетень № 31 ! (45) Дата опубликования описания 26,09.77 (Я) h1. Кл.

6 11 С 15/00

Государственнн и ноннтет баветв Мнннстров ССГР по делам нэабретеннй н открытнй (53) УДК 681.327.6 (088.8) (72) Авторы изобретения

Г, В. Виталиев, Л. Д, Гвинепадзе и P. В. Смирнов (71) Заявитель (54) АССОБИАТИВИОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Известно «ссоци«тнвное запоминаюшее устройство (АЗУ), содержащее адресные з«томинаюшие модули, разрядные шины которых подключены к соответствуюшим детекторам н одним входам схем ИЛИ первой группы, а адресные шипы - к выходам дешифраторов опроса, входы которых подсоединены к соответствующим выходам схем ИЛИ второй группы, входы которых подключены к выходам регистра опроса и регистра маски. тв

Однако это устройство не допускает выполнения в нем логических операций.

Бель изобретения — расширение функциональных возможностей устройства. Достигает ся это. тем, что оно содержит регистры сдви-1а га, выходы которых подсоединены к соответ ствуюшим информационным входам введенных в устройство схем И, управляющие входы которых подключены к введенному в уст ройство дешифратору операций, а выходы Я к другим входам схем ИЛИ первой группы.

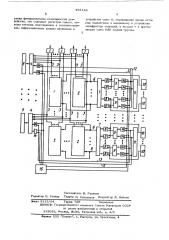

На чертеже показана блок-схема устройства.

Устройство содержит детекторы 1, ад ресные запоминающие модули 2, разряд- Я ные шины 3 которых через схемы ИЛИ 4 первой группы подключены к соответствуюшим входам выходного регистра 5, выпол пенного, например, в виде нескольких ре гистров сдвига. Кроме того, раэряднеяе шины

3 подсоединены к входам детекторов 1. Ад ресные шины 6 модулей 2 соединены с вы ходами соответствуюших дешифраторов 7 опроса, а схемы ИЛИ 8 второй группы включены между входами дешифраторов 7 опроса и соответствуюшими единичными и нулевыми выходами регистра 9 опроса.и единичными выходами регистра 1 О маски. Регистры 1 1 сдвига образуют регистр второго операнда.

Единичные 12 и нулевые 13 выходы perac ров 11 сдвига присоединены к информациоте ным входам схем И 14, управляюшие входы которых присоединены к соответствуюшим выходам дешифратора 15 операций. Выходы схем И 14 подключены к входам схем ИЛИ

4 и регистра 9. опроса.

По способу выполнения поразрядные ло гические операции над двумя операндами могут быть разделены на три группы.

1, Иниртирование, выборка в прямом ко4931 62

Группа операций логического суммирова)О ния выпож яется следующим ооразом. Если в данном разряде регистра 11 находится

"единица (или "нуль" для операций с обратным кодом второго операнда), то этот код передается через соответствующие схе1б мы И 14 и схемы ИЛИ 4 на вход одноименной части выходного регистра 5. В противном случае производится выборка из АЗУ в прямом или обратном коде, в соответствии с тем, в прямом или обратном коде участ»

2О вует в операции первый операнд, Группа операций логического умножения требует обращения к АЗУ при наличии кода "единицы" в данном разряде части регист ра 11 (или ",нуля" для операций в обратном

2б коде); Нулевой код передается непосредст, венно на выходной регистр 5. Таким образом, для выполнения в данном АЗУ любой логической операции достаточно поразрядных операций: выборка в прямом коде, выборка в обратном коде (инвертирование) и передача кода операнда на выходной регистр

5. Если второй операнд также находится в

АЗУ, то перед выполнением основной операции он должен быть выбран на регистр

11. Результат операции может быть передан за один такт с выходного регистра 5 на регистр 11 или записан в АЗУ по любому адресу.

В асинхронном режиме операции логичео4О кого сложения и умножения могут быть ускорены примерно вдвое за счет того что, в среднем, в половине случаев не тре, уется обращений к АЗУ. Используя в АЗУ полу

45 .проводниковые модули с к-1-4 можно полу«

I чить результат любой логической операции, дз, суммирование по модулю два и операция равнозначности.

2. Операции логического сложения для четырех комбинаций из двух операндов в прямом и обратном коде. б

3. Операции логического умножения для тех же четырех комбинаций.

Операции первой группы сводятся к onepasiu поразрядной выборки в прямом и обратном коде - в зависимости от типа операции и кода второго операнда. Рассмотрим более подробно выполнение операции суммирования по модулю два. Подготовка первого операнда заключается в возбуждении шин 3, соединенных с детектором 1, соответствующим порядковому номеру (адресу) этого операнда. Отметим, что разрядные шины модулей 2, соединенные с одним и тем,же детектором соответствуют номеру операнда, а адресные шины - его разрядам, причем, код этого операнда записывается в каждом модуле 2 в виде «единицы« на фоне "нулей и единица записывается в той адресной шине, номер которой соответствует двоичному коду записанного числа. Второй операнд поступает на регистр 11. Для повышения быстродействия регистр 11 разбит на нес колько частей, причем количество разрядов в коде, -хранящемся в каждой такой части, связано с числом адресных шин модулей тз к как rl 2 . Операция выполняется параллельно по слогам за к тактов регистра 11.

Если в младшем разряде данной части регистра 11 находится нуль, то соответствующий разряд кода первого операнда должен быть выбран в прямом коде. Для этого возбуждаются все адресные шины нужного модуля с номерами, соответствующими двоичным кодам адресов, содержащих "единицу в данном разряде, что достигается путем занесения кода 11...10 в соответствующую часть регистра 1 0 маски и кода 1 1 ° ..1 1 через схемы И 14 в соответствующую часть регистра 9 опроса. Необходимые для этого схемы И 14 выбираются с помощью дешиф ратора 15 операций.

Если в младшем разряде находится код единицы, то выборка из АЗУ производится в обратном коде в соответствии с номерами кодов двоичных адресов, содержащих в данном разряде нуль, Для этого на регистр

10 маски заносится код 11...10, а на регистр 9 опроса - код 00...00. В следующем такте код на регистрах 5, 10 и 11 сдвигает . ся на разряд, в регистре 10 циклически, и операция выполняется над вторыми разрядми слогов первого и второго операндов и т. д.

Операция равнозначности выполняется подобным же образом, за исключением того, что наличие "единицы в данном разряде регистра 11 требует выборки из АЗУ в прямом коде, а нуля - в обратном. Операция инвертирования эквивалента операции.0суммирования по модулю два с кодом второго операнда 1 1 ...1 . Занесение на регистр 1 1 кода 00...0 позЬоляет осуществить выбор-. ку из АЗУ в прямом коде, в среднем, за один-три такта обращения к

АЗУ, Формула изобретения

Ассоциативное запоминающее устройство, содержащее адресные запоминающие моду« ли, разрядные шины которых подключены к соответствующим детекторам и одним входам схем ИЛИ первой группы, а адре< » ные шины — к выходам дешифраторов опроса, входы которых подсоединены к соответствующим выходам схем ИЛИ второй группы, входы которых подключены к выходам ре® гистра опроса и регистра маски, о т л ич а ю щ е е с я тем, что, с целью расши493162

Составитель В. Рудаков

Редактор Е. Гончар Техред В, KvnpHHH08 Корректор П. Небола

Заказ 3115/54 Тираж 729 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по. делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r, Ужгород, ул. Проектная, 4 ренин функциональных возможностей устройства, оно содержит регистры сдвига, выходы которых подсоединены к соответствующим информационным входам введенных в устройство схем И, управляющие входы которых подключены к введенному в устройство дешифратору операций, а выходы — к другим входам схем ИЛИ первой группы.