Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 493893

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 12.05.74 (21) 2025211/26-9 с присоединением заявки № (23) Приоритет

Опубликовано 30.11.75. Бюллетень № 44

Дата опубликования описания 01.04.76 (51) М. Кл. Н ОЗЬ 3/04

Государственный комитет

Совета Министров СССР (53) УДК 621.396.668 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. H. Лукин, В. А. Кабанов, В. В. Шкирятов и А. В. Бекетов (71) Заявитель (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ

Изобретение относится к радиотехнике и может использоваться в радиолокации и радиона вигации.

Известно устройство фазовой автоподстройки частоты, содержащее источник входного оипнала, бло к оценки фазы и последовательно соединенные узкополосный фильтр и фазовый детектор.

Однако из-за нестабильности фазового сдвига сигнала в узкополосном фильтре устройство не обеспечивает высокую точность измерения фазы принимаемого сигнала.

Цель изобретения — повышение точности измерения фазы сигнала.

Для этого в предлагаемом устройстве между источ ником вход ного сигнала и входом узкополосного фильтра включены смеситель и первый коммутатор, второй вход которого соединен с входом смесителя, а между выходом фазового детектора и блоком оценки фазы— последовательно соединенные инвертор и второй коммутатор, второй вход которого соединен с входом инвортора, выход блока оценки фазы соединен с вторыми входами смесителя чепосред ствен но, и фазового детектора через делитель частоты, а входы управления коммутаторов соединены с выходом генератора тактов.

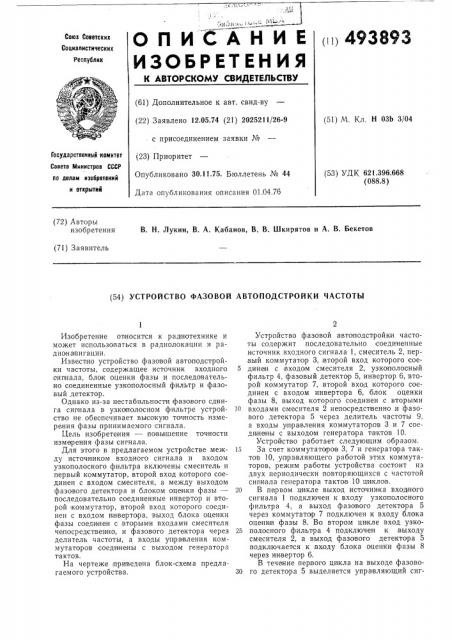

На чертеже приведена блок-схема предлагаемого устройства.

Устройство фазовой àвто подстройки частоты содержит последовательно соединенные источник входного сигнала 1, смеситель 2, пер,вый ком мутатор З,,второй вход которого сое5 дHiHBH с входо м смесителя 2, узкополосный фильтр 4, фазовый детектор 5, инвертор 6, второй коммутатор 7, второй вход которого соединен с входом инвертора 6, блок оценки фазы 8, выход которого соединен с вторыми

10 входами смесителя 2 непосредственно и фазового детектора 5 через делитель частоты 9, а входы управления коммутаторов 3 и 7 соединены с выходом генератора тактов 10.

Устройство работает следующим образом.

15 За счет коммутаторов 3, 7 и генератора тактов 10, управляющего работой этих коммутаторов, режим работы устройства состоит из двух периодически повторяющихся с частотой сигнала генератора тактов 10 циклов.

20 В первом цикле выход источника входного сигнала 1 подключен к входу узкополосного фильтра 4, а выход фазового детектора 5 через коммутатор 7 подключен к входу блока оценки фазы 8. Во втором цикле вход узко25 полосного фильтра 4 подключен к,выходу смесителя 2, а выход фазового детектора 5 подключается к;входу блока оценки фазы 8 через инвертор 6.

В течение перьвого цикла на выходе фазово30 го детектора 5 выделяется управляющий сиг493893 (/(,

Техред Т. Миронова Корректор И. Позняковская

Редактор H. Бутуряна

Заказ 569/15 Изд. № 2020 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 нал, пропорциональной разности фаз входного сигнала Sin (о)сГ+(рс+Л(р2), (где Л(рз— паразитный сдвиг фазы в узкополосном фильтре 4) и сигнала оценки Яп(о),t+q)c), .поступающего с выхода делителя частоты 9 с коэффициентом деления, ра вным 2: — — с с+ +2 — " с+ - 92.

Во время второ-о цикла на вход фазового детектора 5 по ступает разностный сигнал, выделяемый узкополосным фильтром 4, в результате преобразования на смесителе 2 входного сигнала Sin (c)c/+(()c) и сигнала оценки (Яп2(ос(+2(рс), поступающего с выхода блока оденки фазы 8.

При этом на выходе фазового детектора 5 выделяется составляющая управляющего сигнала, пропорциональная разности фаз

::- 2 ",с ","с+ 7г с" с: о -"с+ 9с а на выходе ияверто ра 6 —.пропорциональная разности фаз

Частота коммутации, определяемая генератором тактов 10, выбирается такой, чтобы время каждого .цикла, с одной стороны, было больше постоянной времени узкополосного фильтра 4, а с другой стороны, было меньше постоянсной времени блока оценки фазы 8.

При этих условиях усредненный на интервале постоянной времени блока оценки фазы 8 управляющий сигнал, пропорциональный усредненной разности фаз

10 практи (еоки не за висит от паразитного сдвига фазы сигнала в узкополосном фильтре 4.

Предмет изобретения

Устройство фазовой автоподст)ройки частоты, содержащее источник входного сигнала, блок оценки фазы и последовательно соединенные узкополосный фильтр и фазовый дстектор, о тл и ч а ю щ е е с я тем, что, с целью повыше)-;ия точности измерения фазы сигнала, между источником входного сигнала и входом узкополосного фильтра включены смеситель и первый коммутатор, второй вход которого соединен с входом смесителя, а между выходом фазового детектора и блоком оценки фазы — последовательно соединенные инвер25 тор и второй коммутатор, второй вход которого соединен с входом инвертора, выход блока оценки фазы соединен с вторыми входами смесителя непосредственно, и фазового детектора через делитель частоты, а входы управ30 ления коммуТаторов соединены с выходом генерато ра тактов.