Устройство для сравнения двух кодовых последовательностей

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 493932

Союа Советских

Социалистических

Реслублнк

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02.04.74 (21) 2011277/26-9 с присоединением заявки № (23) Прио,ритет

Опубликовано 30.11.75. Бюллетень № 44

Дата опубликования описания 16.02.76 (5!) М. Кл. Н 041 7/08

Н 031< 19/24

Гасударственный комитет

Совета Министров СССР ло делам иаобрвтений н открытий (53) УДК 621.374.384 (088.8) (72) Авторы изобретения

A. H. Рохмистров, Р. Г. Червен-Водали и Ю. А. Гаевский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВУХ

КОДОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к технике связи и может использоваться в аппаратуре опознавания, системах автопуска и цикловой синхронизации.

Известно устройство для сравнения двух кодовых последовательностей, содержащее линию задержки с ячейками памяти принятых сигналов, линию задержки эталонного сигнала и блок поимпульсного сравнения, каждая ячейка которого включена между соответствующими ячейками упомянутых линий задержки, а также датчик псевдослучайной последовательности.

Однако в известном устройстве не обеспечивается быстрое фазирование при включении.

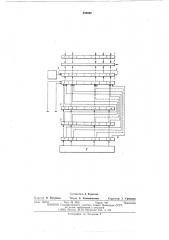

Цель изобретения — ускорение фазирования прп включении, Для этого в предлагаемое устройство введены линии задержки хранения предыдущего, текущего и последующего значений отрезков последовательности, связанные между собой так, что одноименные ячейки первой, второй и третьей линий задержки соединены последовательно, и последняя из них подключена к выходу датчика псевдослучайной последовательности, выходы всех одноименных ячеек подключены к соответствующим входам линии задержки эталонного сигнала через схему коммутации, причем с выхода последней ячейки на вход первой ячейки линии задержки эталонного сигнала введена обратная связь, На чертеже приведена блок-схема предла5 гаемого устройства.

Устройство для сравнения двух кодовых последовательностей содержит линию задержки

1 с ячейками памяти принятых сигналов, линию задержки эталонного сигнала 2, с выхо10 да последней ячейки которой на вход первой ячейки введена обратная связь, блок поимпульсного сравнения 3, каждая ячейка которого включена между соответствующими ячейками линии задержки 1 и линии задержГб ки эталонного сигнала 2, линии задержки 4, 5 и 6 хранения предыдущего, текущего и последующего значений отрезков последовательности соответственно., связанные между собой так, что каждые одноименные ячейки линий

20 задержки 4, 5 и 6 соединены последовательно, и выходы всех одноименных ячеек подключены к соответствующим входам линии задержки эталонного сигнала 2 через схему коммутации 7, два управляющих входа которой под25 ключены к датчику времени, датчик псевдослучайной последовательности 8, выходы которого подключены к соответствующим входам линии задержки 6, и схему выдачи тактовых импульсов 9, подключенную к линии за30 держки эталонного сигнала 2.

3

Устройство работает следующим образом.

Датчик псевдослучайной последовательности 8 и источник псевдослучайной последовательности на передаче работают автономно, синхронно по сигналам, выдаваемым датчиком времени.

С датчика псевдослучайной чоследовательности 8 в дискретные моменты времени на линию задержки 6 записывается отрезок последовательности, соответствующий последующему интервалу принимаемого сигнала. Одновременно записанный на этой линии задержки 6 отрезок последовательности переписывается на линию задержки 5, и, в свою очередь, отрезок последовательности с линии задержки

5 переписывается на линию задержки 4.

Поступающий из канала связи отрезок последовательности, подлежащий сравнению с отрезком датчика псевдослучайной последовательности 8, по и входам (и — число двоичных символов в отрезке) записывается на линию задержки 1.

Одновременно схема коммутации 7 в зависимости от положения момента времени сравнения подключает к входам линии задержки эталонного сигнала 2 выходы линии задержки

4 или выходы линии задержки 5. При перезаписи отрезка псевдослучайной последовательности на линию задержки эталонного сигнала 2 в блоке поимпульсного сравнения 3 происходит его сравнение с принятым отрезком, записанным в линии задержки 1.

В случае их совпадения появляется сигнал эквивалентности на выходе блока попмпульсного сравнения 3.

Если конец приема отрезка совпал с первой половиной дискретного интервала времени смены отрезков псевдослучайной последовательности, то производится сравнение принятого отрезка с отрезком, который соответствует интервалу, предшествующему текущему, а затем с отрезком, соответствующим текущему интервалу. Если .конец присма отрезка совпал со второй половиной дискретного интервала, то производится сравнение принятоro отрезка с отрезком, соответствующим текущему интервалу, а затем с отрезком, соответствующим последующему интервалу. Таким образом, сравнение принятого отрезка произ5 водится дважды.

Схема выдачи тактовых импульсов 9 2п тактовыми импульсами производит циклический сдвиг отрезка последовательности по ячейкам линии задержки эталонного сигнала 2, благо10 даря чему в блоке поимпульсного сравнения 3 осуществляется 2п последовательных сравнений с принятым отрезком. Выбранная частота следования тактовых импульсов исключает возможность смены отрезка в лини.. задерж15 ки эталонного сигнала 2 в течение эт Ix последовательных сравнений. Этим обеспечивается прием отрезков последовательности в случайный интервал времени с длительностью, не меньшей одного отрезка.

Предмет изобретения

Устройство для сравнения двух кодовых последовательностей, содержащее линию задержки с ячейками памяти принятых сигналов, линию задержки эталонного сигнала и блок поимпульсного сравнения, каждая ячейка которого включена междусоответствующими ячейками упомянутых линий задержки, а также датчик псевдослучайной последовательности, отличающееся тем, что, с целью ускорения фазирования при включении, введены линии задержки хранения предыдущего, текущего и последующего значений отрезков последовательности, связанные между собой так, что одноименные ячейки первой, второй и третьей лини) . ".адержки соединены последовательно, и последняя из иих одключена к выходу датчика псевдослучайной последовательности, выходы всех

40 одноименных ячеек подключены к соответствующим входам линии задержки эта, IOHHOго сигнала через схему коммутации, причем с выхода последней ячейки иа вход первой ячейки линии задержки эталонного сигнала введена обратная связь.

Редактор Н. Батурина

Составитель А, Кузнецов

Техред А. Камышникова

Корректор Т. Гревцова

Заказ !42/18 Изд. № 2016 Тираж 740 Подписное

ЦНИИПИ Государственного комитета Сонета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2