Преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (1) 494744

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (51) М. Кл. G 06f 5 02 (22) Заявлено 22.04.74 (21) 2018497/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.12.75. Бюллетень № 45

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.3(088.8) Дата опубликования описания 03.03.76 (72) Авторы изобретения

В. А. Вишняков и А. T. Пешков (71) Заявитель

Минский радиотехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА

В ДВОИЧНЪ|Й

Область применения изобретения — вычислительная техника и системы управления для преобразования десятичного кода целых чисел, в двоичный в устройствах ввода-вывода и преобразования информации.

Известны преобразователи двоично-десятичного кода в двоичный с использованием сдвигающих регистров и блоков коррекции по числу тетрад преобразуемого кода, в котором выходы каждого разряда каждого регистра сдвига через соответствующие вентили соединены со входами элементов «ИЛИ» последующего младшего разряда того же регистра; входы вентилей младшего разряда каждого регистра сдвига соединены с шиной тактовых импульсов, а блоки коррекции выполнены в виде групп схем «И».

Невысокое быстродействие таких устройств обусловлено большой длительностью такта преобразования.

Целью изобретения является повышение быстродействия.

Эта цель достигается тем, что в предложенном преобразователе входы первого элемента «И» и блока коррекции данной тетрады соединены с единичным выходом третьего и нулевым выходом второго младших разрядов регистра сдвига той же тетрады. Вход второго элемента «И» соединен с единичным выходом четвертого разряда регистра сдвига.

Входы третьего элемента «И» соединены с нулевым выходом третьего и единичным выходом второго разрядов регистра сдвига.

Входы четвертого элемента «И» соединены с

5 единичными выходами второго и третьего разрядов, а входы пятого элемента «И» — с нулевыми выходами второго, третьего и четвертого разрядов регистра сдвига. Выход первого элемента «И» соединен через соответ1о ствующие входные элементы «ИЛИ» с единичными входами первого и второго разрядов, выход второго элемента «И» через соответствующий входной элемент «ИЛИ» — с единичным входом первого разряда. Выход

15 третьего элемента «И» соединен через соответствующие элементы «ИЛИ» с единичным входом третьего и нулевым входом первого разрядов, выход четвертого элемента «И»вЂ” с единичным входом четвертого разряда тт

20 через соответствующие элементы «ИЛИ» с нулевыми входами первого, второго и третьего разрядов, а выход пятого элемента «И» через соответствующие элементы «ИЛИ» — c единичным входами первого и третьего раз25 рядов. Входы всех элементов «И» блока коррекции данной тетрады соединены через соответствующий вентиль с единичным выходом младшего разряда регистра сдвига предыдущей старшей тетрады, нулевой выход коЗО торого соединен через соответствующий вен494744

10

Таблица

Выходной двоичный код

Десятки Единицы

Сотни № такта

0101

0001

0101

0011

0011

0001

0000

0001

0101

0001

0000

1

3

5

7

9

0001

0000

01

101

1101

01101

001101

1001101

01001101

101001101

1101001101 тиль со входами вентилей второго, третьего и четвертого разрядов данной тетрады и с нулевым входом четвертого разряда данной тетрады.

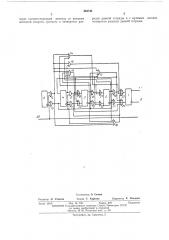

На чертеже приведена функциональная схема одной тетрады, где обозначено: 1 — 4 разряды (триггеры) четырехразрядного регистра сдвига тетрады; 5 — разряд (триггер) младшего разряда соседней тетрады; 6—

11 — вентили второго, третьего и четвертого разрядов, обеспечивающие сдвиг на один разряд вправо кода данной тетрады; 12 — 13— вентили младшего разряда соседней старшей тетр ады; 14 — 18 — соответственно первый, второй, третий, четвертый и пятый элементы

«И» блоков коррекции; 19 — 24 — входные элементы «ИЛИ» разрядов тетрады.

Устройство работает следующим образом.

В исходном состоянии в четырехразрядном регистре сдвига зафиксирован двоично-десятичный код соответствующей десятичной циф ры преобразуемого числа. При поступлении по шине 25 тактовых сигналов в данную тетраду поступает либо сигнал сдвига с выхода вентиля 13, если младший разряд соседней старшей тетрады 5 находится в нулевом состоянии, либо сигнал коррекции с выхода вентиля 12, если разряд 5 — в единичном состоянии. Сигнал сдвига, поступая на вентили б — 11, обеспечивает сдвиг кода тетрады на один разряд вправо. Сигнал коррекции, поступая на элементы 14 — 18, обеспечивает установку в разрядах 1 — 4 тетрады кода, определяемого кодом во втором, третьем и четвертом разрядах тетрады до коррекции.

При кодах 100, 011, 010, 001, 000 в этих трех разрядах до коррекции в тетраде по сигналу с вентиля 12 через схему коррекции происходит установка кодов 1001, 1000, 0111, 0110, 0101 соответственно.

Таким образом, на первом такте обеспечивается сдвиг кода данной тетрады, если нет переноса в эту тетраду единицы из соседней старшей тетрады, или установка в тетраде

65 кода, равного уменьшенному в два раза и увеличенному на пять исходному коду, если в данную тетраду поступает единица переноса из соседней старшей тетрады. Аналогичные действия выполняются на всех последующих тактах, пока полностью не будет выполнено преобразование всего десятичного числа.

В таблице приведены значения кода в тетрадах после каждого такта при переводе десятичного числа 845. При этом двоичный код появляется на выходе младшей тетрады в виде двоичных цифр, начиная с младшей.

Предмет изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий четырехразрядные регистры сдвига и блоки коррекции по числу тетрад преобразуемого кода, в котором выходы каждого разряда каждого регистра сдвига через соответствующие вентили соединены со входами элементов «ИЛИ» последующего младшего разряда того же регистра, входы вентилей младшего разряда каждого регистра сдвига соединены с шиной тактовых импульсов, блоки коррекции выполнены в виде группы элементов «И», отличающийся тем, что, с целью повышения быстродействия, входы первого элемента «И» блока коррекции данной тетрады соединены с единичным выходом третьего и нулевым выходом второго младших разрядов регистра сдвига той же тетрады; вход второго элемента «И» соединен с единичным выходом четвертого разряда регистра сдвига; входы третьего элемента «И» соединены с нулевым выходом третьего и единичным выходом второго разрядов регистра сдвига; входы четвертого элемента «И» соединены с единичными выходами второго и третьего разрядов, а входы пятого элемента «И» — с нулевыми выходами второго, третьего и четвертого разрядов регистра сдвига; выход первого элемента «И» соединен через соответствующие элементы

«ИЛИ» с единичными входами первого и второго разрядов; выход второго элемента «И» соединен через соответствующий элемент

«ИЛИ» с единичным входом первого разряда; выход третьего элемента «И» соединен через соответствующие элементы «ИЛИ» с единичным входом третьего и нулевым входом первого разрядов; выход четвертого элемента «И» соединен с единичным входом четвертого разряда и через соответствующие элементы «ИЛИ» с нулевыми входами первого, второго и третьего разрядов; выход пятого элемента «И» соединен через соответствующие элементы «ИЛИ» с единичными входами первого и третьего разрядов; входы всех элементов «И» блока коррекции данной тетрады соединены через соответствующий вентиль с единичным выходом младшего раз. ряда регистра сдвига предыдущей старшей тетрады, нулевой выход которого соединен

494744

Составитель Э. Сечина

Техред Т. Курилко

Редактор Л. Утехина

Корректор E. Рожкова

Заказ 224/6 Изд. № 130 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 через соответствующий вентиль со входами вентилей второго, третьего и четвертого разрядов данной тетрады и с нулевым входом четвертого разряда данной тетрады.