Ячейка памяти

Иллюстрации

Показать всеРеферат

О П И-(. " М "Н Ж Е

ИЗОБРЕТЕНИЯ

zizz 494767

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-гу (22) Заявлено 22.07.74 (21) 2045i469/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.12.75. Бюллетень № 45

Дата опубликования описания 19.02.76 (51) М. Кл. б lс 11 40

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

И. А. Аракчеева, В. М. Мамута, В. В. Прушинский, А. П. Удовик, Ю. T. Федоров и А. Г. Филиппов (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области вычислительной техники и предназначено для использования в ОЗУ ЦВМ, в частности, имеющих интегральное исполнение.

Известны запоминающие ячейки, содержащие биполярные инжекционные транзисторы. транзисторы хранения, числовые и разрядные шины.

Недостатком известной ячейки является малая величина тока при считывании информации. Это объясняется тем, что в ячейке при считывании и записи происходят одни и те же процессы, и при увеличении тока при считывании возможно разрушение информации, Малый ток считывания обусловливает невысокое быстродействие ячейки и сложность устройств считывания информации.

Целью изобретения является повышение быстродействия ячейки памяти и упрощение схем управления.

Эта цель достигается введением дополнительного инжектирующего n — р — и транзистора и переключающего диода. При этом база инжектирующего n — р — и транзистора соединена с числовой шиной, эмиттер — с шиной смещения и через переключающий диод с об ьедипепными коллекторами транзисторов хранения, к которым подключен также коллектор n — р — и инжектирующего транзистора.

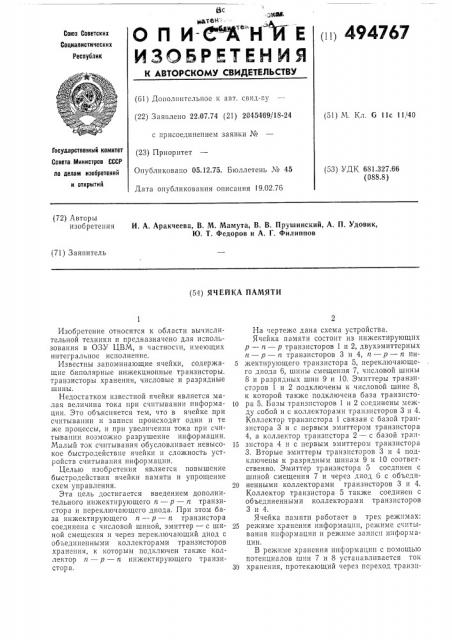

На чертеже дана схема устройства.

Ячейка памяти состоит из инжектирующпх р — п — р транзисторов 1 и 2, двухэмиттерных п — р — и транзисторов 3 и 4, и — р — п ин5 жектирующего транзистора 5, переключающего диода б, шины смещения 7, числовой шины

8 и разрядных шин 9 и 10. Эмиттеры транзисторов 1 и 2 подключены к числовой шине 8, к которой также подключена база транзисто10 ра 5. Базы транзисторов 1 и 2 соединены между собой и с коллекторами транзисторов 3 и 4.

Коллектор транзистора 1 связан с базой транзистора 3 и с первым эмиттером транзистора

4, а коллектор транзистора 2 — с базой трал15 зистора 4 и с первым эмиттером транзистора

3. Вторые эмиттеры транзисторов 3 и 4 подключены к разрядным шинам 9 и 10 соответственно. Эмиттер транзистора 5 соединен с шиной смещения 7 и через диод 6 с объеди20 ненными коллекторами транзисторов 3 и 4.

Коллектор транзистора 5 также соединен с объединенными коллекторами транзисторов

Зzz4.

Ячейка памяти работает в трех режимах:

25 режиме хранения информации, режиме считывания информации и режиме записи информации.

В режиме хранения информации с помощью потенциалов шпн 7 и 8 устанавливается ток

30 хранения, протекающий через переход транзи494767

Предмет изобретения

Составитель P. Яворовская

Техред А. Камышникова Корректор Т. Фисенко

Редактор Л. Утехина

Заказ 196/14 Изд. Ме 129 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 стора 5. Этот транзистор входит в насыщение, его переход база — коллектор (который является одновременно переходом база — эмиттер транзисторов 1 и 2) смещается в прямом направлении, и большая часть базового тока ответвляется за счет инжекции неосновных носителей в этот открытый переход. Ток, протекающий по переходам эмиттер — база транзисторов 1 и 2, вызывает вторичную инжекцию в коллекторы этих транзисторов, являющиеся базами транзисторов 3, и транзисторы 3 и 4 оказываются включенными инверсно. Поскольку один из эмиттеров каждого транзистора связан с базой другого, то при инверсном коэффициенте усиления В )1 ячейка находится в одном из двух устойчивых состояний, т. е. хранит информацию.

В режиме считывания информации напряжение на числовой шине 8 повышается, что вызывает увеличение тока через открытые и насыщенные транзисторы 1 и 3, который идет на заряд паразитных емкостей шины 9. Напряжение на разрядной шине 10 во время считывания меньше напряжения на шине 9 примерно на величину Уо, транзистора 4, так как транзистор 3 насыщен, напряжение между его эмиттерами примерно равно 0, а первый эмиттер его подключен к базе транзистора 4. Паразитная емкость шины 10 заряжается эмиттерным током транзистора 4, который находится в этот момент в активном режиме. Ток первого эмиттера этого транзистора, подключенного к базе транзистора 3, равен О, Током транзистора 3, который может быть достаточно большой величины (экспериментально до 10 — 20 ма), включается усилитель считывания-записи. По окончании считывания напряжение на числовой шине 8 понижается, и ячейка возвращается в режим хранения информации, не меняя своего состояния.

В режиме записи информации повышается напряжение на шине смещения 7, числовой

5 шине 8 и одновременно (с помощью усилителя считывания-записи) фиксируется потенциал на разрядной шине 9. Ток, протекающий через диод 6 и коллектор насыщенного транзистора

3, переводит его в активный режим. Ток кол10 лектора транзистора 2 переключается из эмиттера транзистора 3 в базу транзистора 4 и насыщает его. При снижении потенциалов шин 7 и 8 ячейка переходит в режим хранения информации, изменяя свое состояние.

Ячейка памяти, содержащая два инжектирующих р — и — р транзистора, эмиттеры ко20 торых подключены к числовой шине, базы подключены к коллекторам двухэмиттерных

n — р — п транзисторов, коллекторы — к базам соответствующих и — р — п двухэмиттерных транзисторов, вторые эмиттеры которых

25 подключены к соответствующим разрядным шинам, первый эмиттер первого двухэмиттерного n — р — n транзистора подключен к базе второго, первый эмиттер второго двухэмиттерного n — р — и транзистора хранения

30 подключен к базе первого, отличающаяся тем, что, с целью повышения быстродействия ячейки, она содержит диод и дополнительно инжектирующий n — р — п транзистор, база которого подключена к числовой шине, кол35 лектор к базам р — и — р инжектирующих транзисторов, эмиттер — к шине смещения и к аноду диода, катод которого подключен к базам инжектирующих р — и — р транзисторов.