Усилитель считывания

Иллюстрации

Показать всеРеферат

1ii) 495706

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид,-ву (22) Заявлено 24.05.74 (21) 2028516!18-24 (51) Ч. Кл. G 1lс 7, 06 с присоединением заявки Хе

Государственный комитет

Совета Министров СССР па делам изобретений и открытий (23) Приоритет

Опубликовано 15.12.75. Бюллстснь М 46

Дата опубликования описания 05.03.76 (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

В. Ф. Басалыга, Н, Л. Росина и О. Ф. Щербаков (71) Заявитель (54) УСИЛИТЕЛЬ СЧИТЪ|ВАНИЯ

Изобретение относится к области вычислительной техники.

Известны усилители считывания, содержащие дифференциальный каскад, вход которого соединен с выходом предварительного каскада, а первый выход — через последовательно включенные элемент сравнения и интегрирующий элемент — с входом предварительного каскада, и эмиттерный повторитель.

Недостатком известных устройств является недостаточное быстродействие.

Цель изобретения — повышение быстродействия усилителя считывания.

Для достижения пели усилитель считывания содержит форсиру|ощий элемент и ограничительный элемент, причем второй выход дифференциального каскада связан с входом эмпттерного повторителя, и через ограничительный элемент — с шиной стробирования, а выход эмпттерного повторителя соединен через форсирующий элемент с входом предварппгельного каскада.

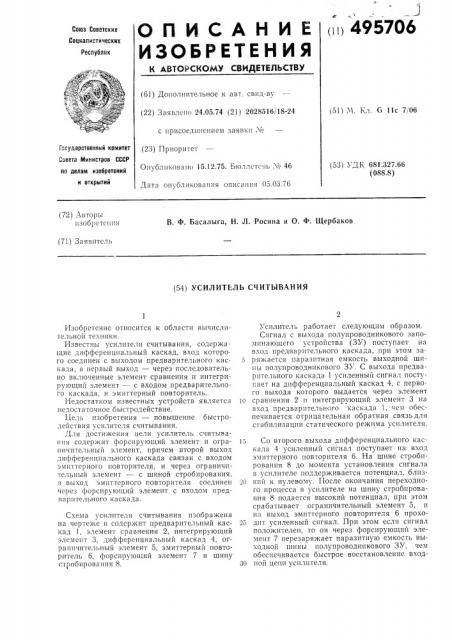

Схема усилителя считывания изображена на чертеже и содержит предварительный каскад 1, элемент сравнения 2, интегрирующий элемент 3, дифференциальный каскад 4, ограничительный элемент 5, эмиттерныи повторитель 6, форсирующий элемент 7 и шину стробирования 8.

Усилитель работает следующим образом.

Сигнал с выхода полупроводникового запоминающего устройства (ЗУ) поступает па вход предварительного каскада, при этом за5 ряжается паразптная емкость выходной шины полупроводникового ЗУ. С выхода предварительного каскада 1 усиленный сигнал поступает на дифференциальный каскад 4, с первого выхода которого выдается через элемент

10 сравнения 2 и интегрирующий элемент 3»а вход предварительного каскада 1, чем обеспечивается отрицательная обратная связь для стабилизации статического режима усилителя.

15 Со второго выхода дифференциального каскада 4 усиленный сигнал поступает на вход эмиттерного повторителя 6. На шине стробированпя 8 до момента установления сигнала в усилителе поддерживается потенциал, близ20 кип к нулевому. После окончания переходного процесса в усилителе на шину стробпровапия 8 подается высокий потенциал, при этом срабатывает ограничительный элемент 5, и на выход эмиттерного повторителя 6 прохо25 дпт усиленный сигнал. Прп этом если сигнал положителен, то он через форсирующий элемент 7 перезаряжает паразитную емкость выходной шины полупроводникового ЗУ, чем обеспечивается быстрое восстановление входЗО ной цепи усилителя.

195706

Фора!уг!!! Изобретения

Со. I а ни I сг(h Б. Фролов

Тсхрсд Е. Митрофанова

Корректор H. Лебедева

Редактор Б. Нанкнна

Заказ 289 12 Из;(. ¹ 2074 Тираж 648 Поди нснос

11111111П11 I ос(с(арс(венного коми гета Говета Мнннсгров ССГР,(o, (c l(!. >(изобре гений H откр(>! (ИЙ

113085, Москва, ?К-З5, Раун(ска!! наб., д. 4/5

Тииог1нн1)и!(, нр. Саи, иова, 2

Усилитель считывания, содержащий дифференциальный каскад, вход которого соединен с выходом предварительного каскада, а перВый Выход — через последовательно включен-!!ые элемент сравнения и интегрирующий элемент — с входом предварительного каскада, и эм1ггтерный повторитель, о т л и ч и ю щ и йс )1 тсм, >1 го, с 1(сс!ь!О II0131>ILH(нн?1 (?ыстРОДсн("! ВИЯ )>СИЛИТ(. 1Я, OII COJ(.P?КИТ ($0PCIIPI>К)ШИИ элемент и ОграHичиTcлыlь1Й элcмснт, причcх1

ВтОрОН I3blxo3, диффере!1пиальHOro

5 cBH:3ан с Входом 3M!I Iт(.pllol IIoBTopIIT(.1R, через ограничительный элемент — с шиной стробирования, а выход эмиттерного повторителя соединен через форсиру10пц!1! элемент с входом нредварителыюго каскада.