Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

iii) 4957I2

Сосз Соеетскии

Социелистичесиих

Республик

1 !

1 (61) Дополнительное к авт. сьид-ву (22) Заявлено 05.04.74 (21) 2013375 18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.12.75. Бюллетень ¹ 46

Дата опубликования опиcàíèÿ 30.03.76

Госудсрстеаниый комитет

Совета Министров СССР оо долом изсоретеиий и открытий (53) УДК 681.327.6 (088.8) (72) Авторы изобретения

В. М. Гриць и О. Г. Светников

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств.

Известно оперативное запоминающее устройство, содержащее накопитель, подключенный к адресному блоку, соединенному со счетчиком адреса, и разрядному блоку, соединенному с одним из входов элемента «ИЛИ», выход которого подключен к первому входу блока сравнения, второй вход, которого соединен с разрядным блоком, блоки контроля, соединенные с накопителем, элементы «И» по количеству разрядов накопителя, одни из входов которых подключены к разрядному блоку, другие — к выходам одного из блоков контроля,,дешифратор.

В известном устройстве не обнаруживаются неисправности функциональных элементов электроники обрамления (усилителей воспроизведения, формирователей адресных и разрядных токов), что снижает надежность работы устройства.

Предлагаемое устройство отличается от известного тем, что оно содержит блок формирования эталонных слов, вход которого подключен к блоку управления, а выходы — к разрядному блоку и другому входу эл-мента

«ИЛ1Л», коммутатор, входы которого подклюJpHbl к выходам о 1ока сравнения, э.г:;i птов

«И», другого блока контроля, блока управления и дешифратора, вход которого соединен с адресным блоком, дополнительный накопитель, входы которого подключены к выходам блока управления и коммутатора, блок анализа статистических данных, входы которого подключены к выходам блока управления и дополнительного накопителя, d выход — к выходной шине устройства, регистр, входы и выходы которого подключены к соответствующим выходам и входам счетчика адреса, в результате чего значительно повышается надежность работы устройства и увеличивается его быстродействие.

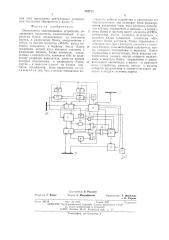

На чертеже изображена структурная схема предлагаемого устройства.

Гб Запоминающее устройство содержит накопитель 1, соединенныи с адресным и числовым блоками 2 и 3, соответственно, блок 4 управления, дополнительньш накопитель 5, коммутатор 6, блок 7 анализа статистических данных (о сбойны: сптуациях), блок 8 формирования эталонных c.loB, дешифратор 9, блок

10 контроля, служащий для обнаружения обрывов разрядных шпн накопителя 1, блок 11 ксптроля, служащий для измерения разряд25 I I bl X T O li0 B > э л е м е H T bl « И» 1 2 3,. ядов, выпол 1яющпе ы1ссте с олоком 1 1 функции конт:.оля разрядных формировате;..:;, э, .мент <;11ЛИ» 13, блок 14 сравнения, фпк; .т ющшi сбои усилите. ей воспропзведе30 нпя, ждущий генератор 15 тактовых импуль495712

65 сов, счетчик, содержащий блок 16 младших разрядов кода адреса и блок 17 старших разрядов кода адреса, регистр, .содержащий блок

18 младших разрядов и блок 19 старших разрядов. Входы адресного блока 2 соединены с адресной магистралью 20, числовой блок 3 подключен к числовой магистрали 21, а блок

4 управления - — к командной магистрали 22.

Вход блока 8 подключен к блоку 4 управления, а выходы — к разрядному блоку 3 и одному пз входов элемента «И. 1И» 13, другой вход которого связан с разрядным блоком 3.

Входы коммутатора б соединены с выходами блока 14 сравнения, элементов «И» 12, блока

10 контроля, блока 4 управления и дешифратора 9, вход которого соединен с адресным блоком 2. Входы дополнительного накопителя

5 подключены к выходам коммутатора 6 и блока 4 управления, а выходы — к числовой магистрали 21 и одному из входов блока 7, другои ход которого соединен с блоком 4 управления, а выход в с выходной шиной 23 устроисти». Входы и выходы блоков 18 и 19 регистр; подключены соответственно к выходà vi и в. OJ,ам блоков 16 и l7 счетчика адреcd. ,Устро ство раоотает следующим образом.

11ри сонаружении факта сбоя в работе устI>o»«rad блок 4 управления выдает в центральныи процессор (на чертеже не показан) сигнал прерывания. Центральньш процессор, анализируя операцию, выполняемую устроиством, может разрешить повторение этой операции, i апрпмер, для коррекции сбоя при зашгсп информации в накопитель 1. Б случае повторного сбоя осуществляется переход на выполнение программы диагностики устройства.

11олучив команду перехода на программу диагнос.пки устроиства, блок 4 управления перепис двает содержимое блоков 16 и 17 счетчика в блоки lb и 19 регистра соответственно.,дин из блоков с летчика, например олок 16 младших разрядов кода адреса, устанавлива тся в пуль, изменяя свое состояние до мом< нта поступления импульса переноса старшег разряда блока 16 в блок 4 управления и прекращения подачи импульсов Hd вход блока 16. латем блок 4 управления устанавливаei в нуль олок I(старших разрядов кода адреса и переписывает eîäåðæèìîå блока 18 i3 олок 16:младших разрядов кода адреса. Импульс и реноса старшего разряда блока 17 также прекращает подачу импульсов на его вход. Il, >i выходе из строя формирователя адресных гоков в блоке 2 блок 14 сравнения выдает сигнал неравенства в каждом разряде каждьш раз при включении этого формирователя.

Если сигнал сбоя отсутствует хотя бы в одном из разрядов при одном из включений этого формирователя, то, следовательно, либо накопитель 1, либо числовой блок 3 неисправны.

К таким неисправностям относятся: обрыв разрядной шины, выход пз строя усилителя воспроизведения и формирователя разрядного

2а

50 тока. Прп обрыве разрядной шины в случае записи нуля на ней падает большое напря>кение е только во в;емя формирования фронтов импульса тока, но и во время формирования вершины импульса. Это свойство исполb зуется ля построения блока 10, служащего для обнару>кения обрывов разрядной шины.

Выход нз строя усилителя воспроизведения прп секцпонпровании выходной шины может бы-.ь обнару>кен при наличии систематических сбоев в данном разряде в случае обращения к ячейкам памяти, выходные шины которых объединены в одну секцию и подключены к этому усили-.елю воспроизведения. Для дешифрации номера секции выходной шины можно использовать адрес запоминающей ячейки, который анализируется дешифратором 9, подключенным к адресному блоку 2.

Структура дсшифратора 9 во многом зав:iспт от организации накопителя 1, но почти всегда для дешифрации номера секции выходной шины требуется не весь адрес, а какая-то его часть, что значительно упрощает построение такого дсшифратора.

1-Iеисправность разрядного формирователя может быть обнаружена при записи уля в данном разряде, в частности при отсутствии импульса тока или при выходе его амплитуды за допустимые пределы. Измерение амплитуды импульса тока в разрядной шине производится блоком 11, который во всех аварийных случаях формирует стандартный сигнал. При совпадении этого сигнала с единичным потенциалом нулевого выхода триггера числового блока 3 на элементе 12 формируется сигнал о неисправности данного формирователя разрядных токов. Диагностика осуществляется как при записи, так и прп считывании информациии.

IlpH записи информации подсчитывается количество нссравпений, формируемых блоком 14 сравнения кода регистра числа числового блока 3 с кодом, воспроизводимым усилителями воспроизведения, подключенными к блоку 14 сравнения через элемент «ИЛИ» 13. 11ри считывании блок 14 ср "âíèâàåò код эталонного слова с выходов блока 8 с кодом, воспроизводимым усилителями воспроизведения числового блока 3.

Ьлок 8 представляет собой цифровой автомат, формирующий последовательность эталонных слов, позволяющих наиболее полно проверп гь 1>азлпчные части устройства. Сигналы с выходов дешпфратора 9, блока 10, элементов «li» 12, блока 14 сравнения поступают на входы коммутатора 6. В зависимости от эти.: сигналов коммутатор 6 добавляет в соответствующий канал дополнительного накопителя 5 единичное приращение. Цикл проверки повторяется необход: мое число раз,, после чего блок 4 управления включает блок 7 ана:шза статистических данных, который обрабатывает данные по программе диагностики устройства. В случае возможности выполне495712

Г !

Ь1 3 4

Составитель В. Рудаков

Техред Е. Митрофанова

Корректоры: Т, Миронова и О. Тюрина

Редактор T. Янова

Заказ 396j16 Изд. ¹ 21 15 Тираж 648 Г!одииспос

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4 5 Типография, пр. Сапунова, 2 ния этой программы центральным процессором последний обращается к блоку 5.

Формула изобретения

Оперативное запоминающее устройство, содержащее накопитель, подключенный к адресному блоку, соединенному со счетчиком адреса, и разрядному блоку, соединенному с одним из входов элемента «ИЛИ», выход которого подключен к первому входу блока сравнения, второй вход которого соединен с разрядным блоком, блоки контроля, соединенные с накопителем, элементы «И» по количеству разрядов накопителя, одни из входов которых подключены к разрядному блоку, другие — к выходам одного из блоков контроля, дешифратор, блок управления, отлич а ю щ ее с я тем, что, с целью повышения наложности работы устройства и увеличения его быстродействия, оно содержит блок формирования эталонных слов, вход которого подклю IpFI к блоку управления, а выходы — к разряд5 ному блоку и другому входу элемента «ИЛИ», коммутатор, входы которого подключены к выходам блока сравнения, элементов «И», другого блока контроля, блока управления и д"шифратора, вход которого соединен с à",рсс10 ным олоком, дополнительный накопитель, входы которого подключены к выходам блока управления и коммутатора, блок анализа статистических данных, входы которого подключены к выходам блока управления и допол15 нптельного накопителя, а выход — к выходной шине устройства, регистр, входы и выходы которого подключены к соответствующим выходам и входам счетчика адреса.