Ячейка памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ С®ИДИ ЙйеаСТВУ

Сто» Соеетскнх

Социалист нческн,х

Феснубйни" (и). 496299

1 !

> 3.Ti

Ч (б1) Дополнительное .к авт.:.свид-ну—

1 (22) Заявлено23.04.73 (2l) 191369?/18-2 1 (г() М. Кл, ч ч 1. Jс ). J /40 с присоединением заявки Х-(63) УДК Оe J.,327..66 (088. 8) Гооударстаанный коннтет

Соаата Мнинотроа СССР по делам нзооретеннй н отнрытнй (23) Приоритет (43) Опуолнковано 25. 12,75 Бюллетень %47 (45} Дата о убликоваиия описания /.03,76

{72) Л втор. изобретения

Ь. /1/1. Ч . 1 Еф ПЮК (71) Заявитель осесоюлный научно-исследовательский и проектно-конструкторский,. институт добы ти угля гидравлическим способом (54) ЯЧЦ .ЙК,л1 ЦДЯЯ П1!

Изобретение относится к вычислительной техиике и дисперсной автоматики и может быть использовано в схемах автоматической блокировки„ включения производственных процессов, Известна ячейка памяти, содержащая ° запоминающие элементы, .на дополняющих биполярных транзисторах динисторного типа, в которой коллектор транзистора р-еа-р-типа через одни резисторы подключен к базе транзистора tt-р-ле -типа и к шине nepsoro источника питания, а кол лектор гранзистора а -р-ю -типа через другие резисторы подключен к базе транзистора р-лер-типа и к шине второго источника питания

Известная ячейеаа памяти, однако, имеет ограниченные функпионадьные возможности и сложную струкгуру устройства с входами записи и входами стирания на этих

3 элементах, реалнец юшего функцию за . IIHcH 1 ВосВВ подачи HB входы сигна лов в строго заданной последовательности или одновременно, которую можно предста вить в следующем виде:

2 у . — тх ° х /х 1 х / 1 /х чх ф

/хvx х /, g .где 1 - оператор двухвходопого триггера.

Для реализации этой функпиии навеет нымп типовыми логическими элементами необходимо (ле} элементов типа триггер (лт-1}элемент типа И (n-4}элемент типа ИЛИ

Вель нзобрвтения - расширение области применения ячейки памяти.

1н Поставленная цель достигается э6 счет

; того, что в ячейке памяти, содержашей эа» помниаюшне. элементы, коллекторы транзи« сторов каждого запоминающего элемента подключены к эмиттерам соответствуюших рр транзисторов иоследуюшего запоминающего элемента, а эмяттеры транзисторов первого аапоминаюшего элемента подключены к

: шинам питания.

Количество эаноминаюших элементов в еб ячейке памяти ограничено только условия° ф! (> ЧЧ

3 ми реалиэаиии (величина рабочего напряжеииц, падение напряжения на переходах эмиттер-коллектор), обеспечивающими необходим .й выходной сигнал.

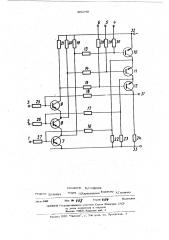

На чертеже изображена схеме ячейки памяти, состоящей иэ трех запоминающих элементов.

Входы 1, 2, 3 являются входами запи си, а входы 4, 5, 6 - входами стирания;

7, 8, A - транзисторы р-Л".р-типа; 10, 10

11, 12 - транзисторы Лр-П-типа;

13 ... 18 - резисторы, соединяющие коилекторы транзисторов с базамн соответствующих транзисторов; 10... 24» резист1ры, соединяющие коллекторы тран- 15 зисторов с шинами питания, 25 ... 30токося раиичивающив резистор; 31 - выхол ячейки, 32, 33 - шийи ь рвого и второго источников питанич.

Транзисторы 7 и 10 н резистор j 3, 20 .16, 19, 22 обра; уют первь A запоминающий эле.",ент. Транзистор"r R и 11 и резисторы 14, 17, 2Р, 23 образуют второй запоминаю лий элемент. Транзисторы 9 и

1Р и пезистор. 15, 18, 21, 24 образу 25 ют третий запоминающий элемент.

Выход последнего з1поиинаюшего эле» мента является основн лм выхочо... ячейки памяти (31).

Ячейка памяти работает следующим образом.

При подаче сигнала ня вход 1 запишется 1 в первый запоминающий элемент, прн подаче сигнала на вход 2 звпишется

1 во второй запоминающий элемент при @ условии, что первый запоминающий элемент находится в состоянии "1".

При подаче сигнала на вход 3 запишется 1" в третий запоминающий элемент при условии, что первый и второй заломи- ® ноющие элементы находятся в состоянии 1 .

Запись "0 (стирание 1 ") происходит одновременно на всех зяпоминакиних элементах при подаче cw вилл на вход 4..11ри и даче сигнала на вход 5 запись 0 производится только во втором и третьем запоминающих элементах, а при подаче сигнала на вхол 6. — только на третьем запоминающем элементе.

При одновременной подаче сигналов на вход записи и стирлння ячейка устанавливается в состояние 0 . Рри установке на входах логического 0 состояние ячейки памяти не меняется.

Входные сигналы могут подаваться чорез герконы. При работе ячейки памяти в сочетании с полупроводниковь1ми элементами сигналы ня входы подаются через диоды, подключенные выводом к базовому резистору.

Формула изобретения

Ячейкл памяти, содержа цая запоминаюLltrtc . элементы ни биполярных транзисторах ди щсторноге типа, в каждом из .которых коллм:rop т(>янэистора р-А»р-типа через одни резисторы подключен к базе транзистора Л-р-й -тиия и к первой шине питания, и коллектор транзистора и-р-и— типа через другие резисторы подключен к базе транзистора р-И-р-типа и ко второй шине питания, о т л и ч а ю ш а я с я тем, что, с полью расширения области применения, в ней коллекторы транзисторов каждого запоминающего элемента подклюе чены к эмиттерам соответствующих тран« знсторов яоследуюшего запол1инающего элемента, 9 эмнттеры транзисторов порвого запоминающего элемента подключены к шинам питания, Состав итеп

1ехРед ПУаранлашова KoPPе"тоP Д.Галахснта

Редактор П 11, Изд. М фЩ Тира к 65ф

lloyd»»cmoe

Заказ 51)HP

Филиал ППП "Патент", г . Ужг. Род, уп. Проектная, 1

1111ИИПИ Государственного комитета Совета Министров СССР но делам иаобретений и открытий

Москва, 113035, Раушская наб., 4