Цифровой интегрирующий вольтметр

Иллюстрации

Показать всеРеферат

ОЛ ИСА НИЙ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДВТВЛЬСТВУ

Coca Севетекик

Сециалиетииеаки1!

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено05.01.72 (2!) 1734755/18-10 (51) М. Кл.

С- 011 19/26

Н 03k 13/20 с присоединением заявки № (23) Приоритет

Государственный намнтет

Саввта Мнннстрав СССР аа делам нзабретеннй н аткрытнй (63) УДК 62 1.3 1 7. 7 (088. 8) (43) Опубликовано25.12.75 Бюллетень №47 (45) Дата опубликования описания 12.03.76 (72) Авторы изобретения l0. В Блинков, Е. A. Г!омтев, В. M. Тихонов и В. М. !!!ляндин (71) Заявитель

Пензенский политехнический институт (54) Циф! ОВОй ИНТЕП И!УЮЩИЙ ВОЛЬтМЕ11

Изобретение относится к области электроизмерительной техники.

Известны интегрирующие цифровые вольтметры, содержащие сумматор измеряемого и компенсирующего напряжений, интегратор, блок выделения периода помехи, распределитель, задатчики временных тактов, ключевые схемы, блок пороговых элементов, преобразователь "Код-напряжение" и логические схемы.

Цепь изобретения - повышение точности измере>шя при максимально допустимой амплитуде помехи и бысчродейстьия при повышегвш частоты помехи.

Э1 о достигается тем, что в предложен- 1н ном устройстве к выходам задатчиков временных тактов, входы которых подключены к выходам блока выделения периода помехи, с>вязанного через переключатель с входом прибора, подсоединены: схема И-НЕ, выход 20 когорой связан с входом удвоения крутизнаl преобразования интегратора, а через григгер — с входом "Г>азрещение запуска" блока выделения периода помехи; через схему сборки задних фронтов импульсов и И триггер со счетным входом — формироват<ч» строб-импульсов, выход которого соединен со входом распределителя, а через схему сборки — ключевая схема, через которун> выход сумматора соединен со входом интегратора, выход которого связан с блоком пороговых элементов через усиля> ель постоянного тока с дискретно изме-няемым коэффициентом усиления, вход>,< управления которого подключены к распределителю.

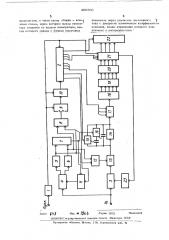

На чертеже изображена структурная схема вольтметра.

Вольтметр содержит схему 1 сброса, распределитель 2, сумматор 3, блок 4 выделения периода помехи, задатчики >, 6 временных тактов, схему 7 И-Н1=, < хаму 8 сборки, триггер 9, схему 10 форми!>овин><>< строб-импульсов, триггер 1 1, < хему 1 2

ИЛИ, ключевую схему 13, ингегратор, состояп<ий из усилителя 14 постоянноги т<>к >, ключевых схем 15, 16 и равных по ве>шчине конденсаторов О, усилитель 17 постоянного тока (У1!Т) с диск!>етш> и;><<в<»< . мым коэффициентом усиления, блок 18 «> роговых элементов, схему 19 выборки

496500

3 ° старшего сработавшего порогового элемента, шифратор 20, блок 21 запоминающих устройств (ЗУ), блок 22 цифрового отсчета, преобразователь 23 - "Код-напряжение", Прибор работает следующим образом. 5

Под воздействием импульса "Пуск" осуществляется возврат в исходное положение триггера 9, блока ЗУ 21, триггера 11, с выхода которого выдается сигнал "Запрет" на запуск блока 4 выделения периода по- 10 мехи. Импульсом Пуск" одновременно запускается схема IO формирования стробимпульса, по заднему фронту. которого срабатывает ключевая схема 15, разряжаю щая конденсатор в цепи обратной связи ин- !5 тегратора и устанавливающая распределитель 2 в положение, соответствующее оценке первого разряда. Распределитель 2 устанавливает значение коэффициента усиления

УПТ 17, необходимое для оценки первого Ю разряда. Срабатывает триггер 11, снимая сигнал "Запрет" с блока 4 выделения перио да помехи, и сигналы с его выходов посту» нают на входы задатчиков 5, 6 временных тактов. 25

Сигнал на запуск задатчика 5 временных тактов будет выдан в момент начала положительного нолунериода сигнала помехи, а в момент начала отрицательного полупериода будет выдан сигнал на запуск задатчи- З ка 6 тактов, и начнется второй такт интегрирования, llo заднему фронту второго временного такта через схему 1 2 И ЛИ выдается сигнал, и ключевая схема 13 переходит в состояние

"Выклк чено".

По этому же фронту через схему 8 сборки выдается сигнал; вызывающий повтор- ное срабатывание трип ера 9, на его выходе появляется сигнал, который запускает схему

l0 формирования строб-импульса. В момент окончания второго такта напряжение на выходе интегратора не зависит от периодической помехи.

I с 4,5

Перепись показаний блока пороговых элементов, подключенного к выходу УПТ 17, производится строб-импульсом через схему

19 выборки старшего сработавшего орогового элемента и шифратор 20 в старший разряд блока ЗУ 21. Блок 21 через преобразователь "Код-напряжение" включает комненсируюшее напряжение, соответствующее коду старшего разряда. По заднему фронту строб-импульса происходит разряд емкости ак интегратора, перевод распределителя 2 на оценку следующего разряда. В свою очередь распределитель 2 изменяет величину коэффициента усиления УПТ 17 для оценки следующего разряда, срабатывает триггер 11, 60 в результате чего сигнал "Запрет" с блока

4 выделения периода помехи снимается.

Оценка следующих разрядов происходит ана логично. После оценки последнего разряда по заднему фронту строб-импульса происхо- дит включение блока 22 цифрового отсчета.

В случае наводки от сети 50 гц информация о периоде помехи может быть выделена непосредственно из сети. Если частота помехи увеличивается, то возможно перекрытие тактов интегрирования. В этом случае для сохранения помехоустойчивости, крутизну интегратора на время перекрытия тактов необходимо удвоить. Для этого с выхода схемы 7 И-НЕ выдается сигнал, который переводит ключевую схему 16 в состояние "Выключено., один иэ конденсаторов С отключается, в результате чего крутизна интегратора на время перекрытия тактов удваивается. Одновременно тот же сигнал вызывает срабатывание триггера 11, и на блок 4 выделения периода помехи выдается сигнал "Запрет" на запуск, который снимается тольке в начале следующего такта измерения, По заднему фронту задатчика временного такта через схему 8 сборки выдается сигнал, вызывающий срабатывание триггера 9. По этому же фронту сигналом с выхода схемы 7 И-НЕ ключевая схема 16 переводится в состояние "Включено", и интегоирование продолжается с нервоначальной крутизной.

Формула изобретен ия

Цифровой интегрирующий вольтметр, содержащий сумматор измеряемого и компенсирующего напряжений, интегратор, блок выделения периода помехи, распределитель, эадатчики временных тактов, ключевые схемы, блок пороговых элементов, преобразователь "Код-напряжение" и логические схемы, о т л и ч а ю ш и и с я тем, что, с целью повышения точности измерения нри максимально допустимой амплитуде помехи и быстродействия при повышении частоты помехи, в нем к выходам задатчиков временных тактов, входы которых подключены к выходам блока выделения периода помехи, связанного через переключатель с входом прибора, подсоединены: схема И-НЕ, выход которой связан с входом удвоения кру"иэны преобразования интегратора, а через триггер — с входом

"Разрешение запуска" блока выделения периода помехи; через схему сборки задних фронтов импульсов и триггер со счетным входом - формирователь строб-импульсов,: выход которого соединен со входом рас496500 пределителя, а через схему сборки — клю- чевия схема, через которую выход суммагора соединен со входом интегратора, выход когорого связан с блоком пороговых

-Тираж 902

Подиисиое!!!!!!!!Г!!! Государственного комитета Совета Министров СССР!!редириятие «Патент», Москва, Т-59, Бережковская иаб. 24

Ъ!

Заказ элементов через усилигель постоянного тока с дискретно изменяемым коэффициентом усиления, входы управления которого подключены к распределителю.