Вычислительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социаямстнмеских

Уеснубнмн (и! 496554 (61) Дополнительное к авт. свнд-ву (22) Заявлено 26,06.73 (21) 1937362/18-24 с присоединением заявки № (23) Г1риоритет (43) Опубликовано26.12.75 Бюллетень ¹ 47 (45) Дата опубликования описания О6 О4 7 (5Ц М. Кл. (06 t 7/38

Гооуавротавиимй комитет

Совета Мииистрое СССР ао двлам изобретений и открытий (N) УДК

681,325 5 (088.8) (72) Автор изобретения

А. А. Мельников (71) Заявитель (54) ВЫЧИСЛИТЕЛЪНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в уст ройствах обработки информации.

И звестны устройства, выполняюшие ариф- к метические операции, содержащие счетчики, 1дешифраторы, элементы задержки, счетчик

;результатов, генератор тактовых импульсов,,выход которого соединен с первым входом

;первого элемента И, выход которого соеди- 1р

;нен раздельным входом первого счетчика,,разрядные входы которого подключены к вы, ходам первой группы элементов И, первые входы которых соединены с регистром, а вторые входы — к выходу первого счетчика да и к раздельному входу второго счетчика,,выход которого через первый дешифратор подключен ко второму входу первого

"емента И и к первому, входу второго эле-, мента И, выход которого подключен к пер вым входам второй группы элементов и не осредственноо, а через первый элемент за, держки - к первому входу счетчика резуль татовв, выходы которого соединены со вто,рыми входами. Второй группы элементов И, 25 выходы которых подключены к разрядным входам второго счетчика.

Такие устройства, однако, могут вымол нять Только отдельные арифметические опе-, рации.

Е1елью изобретения является расширение функциональных возможностей устройства, Это достигается тем, что устройство со !

1 держит дополнительный элемент И, элемент, ИЛИ и блок памяти, вход которого соеди1 нен с первым входом счетчика результатов,,второй вход которого подключен к выходу .первый вход которого соединен с выходом, первого элемента И, второй вход ««с выхсл дом дополнительного элемента И и с раздельным входом третьего счетчика, разряд ные входы которого соединены с блоком, па мяти, в выход через второй дешифратор со единен со вторым входом второго элемента

И и с первым входом дополнительного эле мента И второй вход которого через второй элемент задержки соединен с выходом гене . ратора тактовых импульсов.

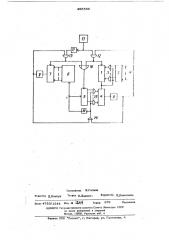

На чертеже представлена схема устро4.—

; ства.

4965, Ь

Оно содержит счетчик 1, соединенный

1 .,параллельными шинами с регистром 2 через группу элемейтов И, счетчики 4, счетчик результатов 5, ф (@ амяти 6, счетчик

„,дешифраторы b<„g эл менты задержки 10, 5

r ч 1М "

14) ЬййуяФ " Х.а, 13, 14 группу элементов И. 15, элемент ИЛИ 16, генератор тактовых импульсов 17. 11а вход 18 подается код аргумента. Вычислитель ое устройство предназначается дпя вычисления функций 10 вида: Л =а„J(, а,х а, -а„

Рассмотрим работу устройства на при4

4 элемент задержки 11 сбрасывается в «0», Одновременно поступает сигнал в блок памяти 6, по которому в счетчик 7 выводится код Я . С разу после этОГО начинае Р ся формирование выражения, стоящего в квадратных скобках, результат снова переносится в счетчик 4. Г!о команде обнуления счетчика 7, которая следует после вывода из счетчика 7 кода Q, производится списывание результата вЛисления со счетчика 5. Элемент задержки ll обеспечивает сдвиг импульсов прп одновременном их суммировании в счетчике 5., мере вычислеяля ллнот"Очлена для случая

I =4, Г(риведенное выражение можно записать """ у-(f fa,x а,1x а,1x a,jx и, Это выражение положено и осно зу работы устройства, 11педварительно «з счет гик 1 и регистр 2 заносится значение )(, в счет чик 4 значение Q, в счетчик 7 значение

Q,, Q в ячейки $>rroKA памяти — значения коэ фпоиентов И вЂ” Q . В общем случае

2 О в счетчик 4 заносится значение 2 в сч -тр) чик 7 значение Й а в ячейки блока паrr-r мя ти коэффициенты Й. + 1, 1исло ячеек

rr2 О

rrBMBTIr долзкно бьrTr ра rrbih $ --. 17 + 1 - 2 =

= М- l, Счет"<ик 5 нредвпрртельно устанавливается в нуль, После того, как в счетчики 4 и 7 заносятся коды, дешифраторы нулевого состояния 8 и 9 открывают элементы 12 и 13. Импульсы с частотой

/ =-, — с выход» генератора1 17 пск тупают т Т

Н8 вычБтаюшие счетчики 1 и 7 и на счеч ик результатов 5 через элемент ИЛИ 16.

Через время Т =-ТтХ счетчик 1 переполняется и с его выхода сигнал поступит на вычитающий счетчик 4 и перепишет код из регистра 2 и счетчик,1. Через время

Т„=Т1 й4=Т Ц.4Х счетчик 4 установится в О", и д шифратор 8 закроет элемент 12. Счетчик 7 установится в нуль через время ТЗ=Т 23, и дешнфт ратор 9 закроет элемент 13, 3а время

Т2 в счетчик 5 поступит 1У1

Й4 импульсов, а за время Т3 в

Т счетчик 5 поступит И - Я

7 импульсов . Всего поступит N = Й4Х +03 импульса, так как сформируется код выражения, стоящего в круглых скобках. Как только счетчики 4.. и 7 встанут в «О», сигналом с элемента 14 код из счетчика

6 переписывается через группу элементов И 15 в счетчик 4, а счетчик 5 через

Формула изnáðетения

Вычислительное устройство, содержащее счетчики, дешифраторы, элементы задержки, счетчик результатов, генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен с раздельным входом пер вого счетчика, разрядные входы которого подключены к выходам первой группы элементов И, первые влоды которых соединегггг с регистром, а вторые входы — к выходу первого счетчика и к раздельному входу

30 второго счетчика, выход которого через первый дешифратор подключен ко второму входу первого элемента И и к первому âõî ду второго элемента И, выход которого под« ключен к первым входам второй группы элем, нтов И, выход которого подключен к первым входам второй группы элементов И непосредственно, а через первый элемент задержки -, к первому входу счетчика результатов, выходы которого соединены со вторыми входами второй группы элементов И, выходы которых подключены к разрядным входам второго счетчика, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей устройства, оно содержит дополнительный элеменг, И, элемент ИЛИ и блок памяти, вход которого соединен с первым входом счетчика резуш татов, второй вход которого подключен к выходу элемента ИЛИ, перв.яй вход которого соединен с выходом первого элемента И, второй вход - с выходом дополнительного элемента И и с раздельным входом третьего счетчика, разрядные входы которого .соединены с блоком памяти, а выход через второй дешифратор соединен со вторым входом второго элемента И и с перввiм r входом дополнительного элемента И, вто рой вход которого через второй элемент задержки соединен с выходом генератора

6О тактовых импульсов.

496554

4Р

Заказ 4750/l244 Изд. М l> f Тираж 679

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, ll3035, Раушская наб., 4

Подписное

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Составитель Э.Сечинв

РедактоР Д,Пинчук ТехРед H.Ханеевп КоРРехтоР ll,Дениокина