Матричное вычислительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

СОюз СОъетских

Сощмалмстическмх ееесвублик (61) Дополнительное к авт. свид-ву(22) Заявлено15.02.74 (21) 1997873/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.12,75 Бюллетень № 47 (45) Дата опубликования описания О6 О4 7

Гооударстеенный иомнтет

Совета Инниотрое СССР

II0 делам изобретений и открытий 7?) Автор изобретения

B. В. Коломейко

Ордена Ленина институт кибернетики АН Украинской ССР (71) Заявитель (54) МАТРИЧНОЕ ВЪ|ЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах, работаюших, как в позиционных системах счисления, так ,: и в непозиционных системах счисления оста- З точных классов. Известно матричное вычислительн6е л, устройство, еодержашее матрицу конъюнктив ных элементов и выходной блок конъюнктив ных и дизьюнктивных элементов, в котором

1, :операнды поступают на входы матрицы коньюнктивных элементов в таком же порядке, в

"каком они поступают на входы данного устройства, т.е, независимо от того, какой из операндов больше и какой меньше, !

Белью изобретения является уменьшение аппаратурных затрат и увеличение быстро, действия устройства.

Поставленная цель достигается тем, что в устройство введен блок расстановки one- gp рандов и блок равенства операндов, входы которых соединены с соответствуюшими входами устройства, входы матрицы коньюнктивных элементов подключены к соответ-! ствующим выходам блока расстановки опе- 25 рандов, а выходы - к соответствующим пер вым группам входов блоков дизъюнктивных элементов операций сложения и умножения,, t вторые группы входов которых соединены с соответствуюшими выходами блока ра венства операндов, а выходы - соответст-, венно с первым и втбрым выходами устрой ства.

Рассмотрим, например, операцию сложения целых чисел А и В. Матрица операции сложения симметрична относительно свое№ . !

» главной диагонали. Если (O«P, О В<Р), то симметричность матрицы позволяет oriределять не все ее Р значений, а только

Ы

1 значений. Для этого слагаемые

2 А и B заменяются слагаемыми Х и У, на которые накладываются следуюшие orpaHH ченйя:

Х=А; У В если А В

Х В; У А > еслиА(В

Для реализации матрицы операции сложения операндов Х и У требуется почти в два раза меньше конъюнктивных элеме

496855 тов, чем для реализации матрицы сложециа операндов А и В.

При этом количество входов дизъюнк ; тивных элементов, объединяющих выходы матрицы конъюнктивных элементов, умень 5 шается также почти в два раза. Это ана- логично и для других операций, подчияяюаихся коммутативному закону, в . ToM числе .и для операции умножения.

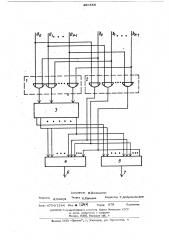

Иа чертеже изображена схема предлагае- 10

, мого устройства.

Оно содержит блок 1 расстановки операндов, блок 2 равенства операндов, мач рицу 3 кожюнктивных элементов, блок 4 дизъюнктивных элементов операций сложе- 15 ния, блок 5 дизъюнктивных элементов опе"рации умножения.

В оды 6 0 g единени с входами блоков 1 и 2. Выхо-t ® ды блока 1 соединены с входамн матрицы 3..

Выходы блока 2 и матрицы 3 соединены с входами блоков 4 и 5. Выходы 6 блока 4 и выходы 7 блока 5 являются выходами устройства.

И

Блок 1 содержит P двувходовых эле- ментов ИЛИ, блок 2 - P двувходовых эле ментов И; матрица 3 .Щ-,.11. двувходо2 вых элементов Й., Операнды А и В. в унитарном коде поступают соответственно по шинам| о Р 1 bî- Р 1 " х д" бл ков 1 и 2. Причем на входы И и Ь (04: t @АР-1, Ос j 4Р-1) сигналы посту- лают только в том случае, если А** t

Ва

Если операнды не равны (АФ В), то на выходе блока 1 возбуждаются две шины, номера которых совпадают с величинами операндов. Сигналы по этим возбужденным

;шинам поступают на входы матрицы 3. Эле . мент И матрицы 3, находящийся на пересечении возбужденных шин, пропускает эти сигналы,,и они проходят на входы блоков

4 и 5. С выходов 6 блока 4 снимается сумма, а с выходов 7 блока 5 снимается произведение операндов А и В.

Блок 2 в этом случае в получении результатов нв участвует, так как сигналы, представляющие операнды А и В на выход блока 2, не проходят.

Если операнды равны (АВ), то на выходе блока 2 возбуждается шина, номер которой равен величине любого,из них. Сигналы по этой возбужденной шине поступают на входы блока 4 и блока 5. С выхоАоВ 6 блока 4 снимается сумма, а с выходов 7 блока 5 снимается произвг.дение операндов А и В, Блок 1 и матрица 3 в этом случае в получении суммы и произведении не учась вуют, так как при равенстве операндов возбуждается только одна шина на входе мат рицы конъюнктивных элементов 3. Сигнал при этом на выход матрицы 3 не проходит и на величину суммы и произведения не влМяет.

Для выполнения других операций, подчиняющихся коммутативному закону, необходимо добавить дополнительные блоки дизъюнктивных элементов соответствующих операций. Работа устройства при этом аналогична описанной выше.

Формула изобретения

Матричное вычислительное устройство, содержащее матрицу конъюнктивных элементов и блоки дизъюнктивных элементов операций сложения и умножения, о т л и ч а ю ш е» с е с я тем, что, с целью уменьшения аппа ретурных затрат и повышения быстродейст, вия, оно содержит блок расстановки операндов и блок равенства операндов, входы которых соединены с соответствующими входами устройства, входы матрицы конъюнк- . тивных элементов подключены к, соответствующим выходам блока расстановки операндов, а выходы - к соответствующим первым группам входов блоков диэъюнктивных элементов операций сложения и умножения, вторые группы входов которых соединены с соответствующими выходами блока равен-ства операндов, а выходы - соответственно с первым и вторым выходами устройства.

496556

Составитель Ц (олометко

Ред к ор д П1, Техреду д.) анеева

Корректор Т.Добровольская

ЫНИИПИ Гасударственного комитета Совета Министров СССР ио делам изобретеиий и открытий

Москва, II3035, Раушсхая иаб., 4

Филиал ППП "ГЬтент, г. Ужгород, ул. Проектная, 4

Заказ 4754/1244 Изд, И ЪЧ 1ираж 679

Подписное