Усилитель фазовых сдвигов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (11) 496662

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистииеских

Уеспу блик . l (51) М. Кл.Н 034 7/18

Н ОЗЬ 3/04 (61)Дополнительное к авт, свид-ву (22) Заявлено 03.04.74 (21} 2013300/26-9 с присоединением заявки № (23) Приоритет (43) Опубликовано.26 12 76. Бюллетень № 47 (45) Дата опубликования описания 25.02.76

Государственный номитет

Соавта Министров СССР ао делам изобретений и открытий (53) УДК 621,396.662 (088.8) (72) Авторы изобретения

В. И. Костенко и В. С. Суздаль (71) Заявитель (54) УСИЛИТЕЛЬ <ИЗОВЫХ СДВИГОВ

Изобретение относится к измерительной технике, радиотехнике и автоматике.

Известен усилитель фазовых сдвигов, содержащий фазовый модулятор и два фазовых детектора, один из которых подключен к 5 источнику опорного напряжения и входу фазового модулятора, а другой — к источнику опорного напряжения и выходу фазового модулятора, Однако известный усилитель имеет зна- )О чительные фазо-частотные и амплитуднофазовые погрешности.

11ель изобретения — уменьшение амплитудно-частотно-фазовых погрешностей.

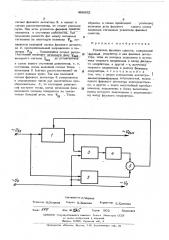

Для этого выход одного фазового детэк- l5 тора непосредственно, а другого через масштабный преобразователь подключены к блоку вычитания, выход которого подсоединен к управляющему входу фазового модулятора. 20

На чертеже приведена структурная электрическая схема усилителя.

Усилитель фазовых сдвипов состоит из фазового модулятора 1 и фазового детектора 2, подключенного к источнику опорного напряжения (06 ) и входу фазового модулятора 1 (Ц ), к выходу фазовоги модулятора 1 подключена пепь, состоящая из последовательно соединенных второго .фазового детектора 3, масштабного преобразователя 4 и блока вычитания 5, второй вход котороро соединен с выходом фазового детектора 2. Выход блока вычиташи 5 подключен к управляющему входу фазового модулятора 1.

Усилитель фаоовых сдвигов работает следуюшим образом.

В исходном состоянии входные гармонические сигналы усилителя 1) и 06 о ах находятся в квадратуре, т. е. сдвинуты по фазе на Т /2, при этом выходной сигнал фазового детектора 2 равен нулю. Выходной сигнал фазового детектора Э уменьшается в определенное число раз масштабным преобразователем 4 и вычитается из

1 выходного сигнала фазового детектора 2.

Сигнал paccor ласования с выхода блока вычитания 5 изменяет начальную фазу выходного сигнала до тех пор, пока выходной

496682 (оставитель я т3ерняк

ТехРед 14. (анеева корректор E.)(мелева

Редактор И.Острова г

Изд. М Id995, Тираж 902 Подписное

Заказ Ю .

ЦНИИГ111 Г осударствеииого комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская паб., 4

Предприятие «Патент», Мос ква, Г-59, Г>ережковская паб., 24

3" сигнал фазового детектора 3, а значит и сигнал рассогласования, не станут равными

,нулю. При этом усилитель:фазовых сдвигов находится в состоянии равйовесия. При . изменении разности фаз между входными сигналами на некоторую величину 1 1 „ появляется выходной сигнал фазового детектора 2, пропорциональный направлению и величине РОГ . Появившийся сигнал растр» гласования изменяет начальную фазу И 1 1О выходного сигнала iJ до установления

8 1Х в схеме нового состояния равновесия, т. е. состояния, когда выходной сигнал блока вычитания 5 (сигнал рассогласования) не с;анет равным нулю. Так как выходной сигнал фазового детектора 3 уменьшается в определенное число раз масштабным пре- . образователем 4, то состояние равновесия наступит тогда, когда начальная фаза . выходного сигнала повернется на значительно больший угол, чем ф . Таким

4 образом, в схеме происходит -. усиление величины угла фазового сдвига между входными сигналами усилителя фаоовых сдвигов;.

Предмет изобретения

Усилитель фазовых сдвигов, содержащий фазовь1й. модулятор и два фазовых детектора, один из которых подключен к источ нику опорного напряжения и входу фазово: го модулятора, а другой - к источнику опорного напряжения и выходу фазового модулятора, отличающийся тем, что., с целью уменьшения амплитудно-частотно-фазовых погрешностей, выход одного фазового детектора непосредственно, а другое — через масштабный преобразователь подключены к блоку вычитания, выход которого подсоединен к управляющему входу фазового модулятора.