Устройство задержки широтно-импульсного сигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

4хеслублик (13)496668 (61) Дополнительное к авт. свнд-ву (22) Заявлено13. 10.73 (21) 1892692/26-2 1 с присоединением заявки № (23) Приоритет(43) Опубликовано 2 5 12 75 Бюллетень №47 (45) Дата опубликования описаиия29.03.76 (51) М. Кл. тт 03k 5/13

Государственный комитет

Сввета Миниетрав СССР во делам изобретений а вткрмтий (53) УДК 621.374.5 (088.8) (7l) Заявитель Московский ордена Ленина и ордена Трудового Красного знамени государственный университет им. М. В. Ломоносова (54) УСТРОЙСТВО ЗАДЕРЖКИ ШИРОТНО-ИМПУЛЪСНОГО СИГНАЛА

Изобретение может широко использовать . ся в моделирующих аналого-цифровых комплексах, в статистических системах, в системах автоматического управления и те де 5

Известны устройства задержки широтgo-импульсного сигнала (ШИС), содержащие входной формирователь, сдвигающие регистры с ключевыми схемами, интеграторы и схемы сравнения, элемент задерж- i0 ки в sstne счетчика и схемы совпадения, собирательную схему и триггер. Однако широкое использование этого устройства ограничивается большой погрешностью в

: формируемом (задержанном) ШИС. 15

Для. повышения точности и величины задержки зходы интеграторов соединены с источниками постоянного отрицательного и положительного напряжения через ключевые схемы, управляющие входы которых 20 . соединены с выходами соответственно первого и второго сдвигающих регистров, входы которых связаны с выходом входного формирователя, причем вход первого—, непосредственно, 8 второго — через эле- 25 мент задержки, выходы интеграторов подсоединены ко входам схем сравнения, выходы которых через собирательную схему подсоединены к одному входу триггера, второй вход которого подсоединен к источнику входного сигнала.

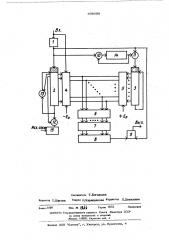

На чертеже дана функциональная схема

:устройства задержки ШИС, Устройство содержит дифференцирующую ,цепочку 1, два сдвигающих регистра 2 и, 3, две группы гключевых схем 4 и 5, группу интеграторов 6, группу схем 7 сравнения нуль-органов, собирательную . схему 8 и триггер 9. Кроме того, в устройстве используются схемы 10-13совпадения, счетчик 14 и триггер 15.

Устройство задержки ШИС работает, следующим образом. Входные .. ШИС диф ференцируются по тактовому фронту в цепочку и подают-я на сдвигающий регистр . 2, который совместно с группой ключа . схем 4 образует входной коммутатор груп пы интеграторов 6 по постоянному источ нику напряжения . Е, где тъ-число так тов за период задержки. Ключевыми схема (72) Авторы изобретения В. Ф. Арховский, В. H. Жовинский, В. А. Попов и О.Г. Калиниченко

496668 ми 4 управляет также входной ШИС. На каждом 4 -ом интеграторе образуется напряжение, пропорциональное длительности

l -го импульса ШИС. Счетчик 14 устанавливают вручную переключателем или автоматически - цифровым кодом с цифрового устройства на заданное время задержки

7 =3, В исходном состоянии схема

10 совпадения открыта, а схема 11 - за-; . крыта. Счетчик 14 при включении устройства начинает считать. По достижении

Т . tl 5 З,,где Т - такт ШИС схема совпадения 10 закрывается, а схема 11открывается. Начинает работать сдвигающий регистр 3, который совместно с ключевыми схемами,5 образует входной коммутатор групйы интеграторов 6-по постоянному источнику напряжения, +E". Нао пряженне на кокденсаторе Е го интегра тора начинает разряжаться линейно (так как + E СОМ Я 7 ) . По достижении о нулевого уровня срабатывает g -ая схема 7 сравнения, импульс с которой пере;дается в собирательную схему 8. Время от начала мхта начало разряда до срабатывания пропорционально начальному напряжению на конденсаторе . -го интегратора (а оно было пропорционально длительности g -го импульса ШИС). Таким образом, с выхода .риггера 9,. на один вход которого подаются импульсы такта со схемы дифференцирования 1, а на второй вход «импульс со схемы собирательной 8, снимаются UIHC с задержкой на

У -Т э о

В исходном состоянии схема совпаде5. ния 13 открыта, а схема 12 закрыта. Если время задержки оказывается больше, чем Т б, некоторые импульсы входного ШИС выпадают из выходного сигнала.

Для сигнализации "переполнения" служит схема 12 совпадения и триггер 15.

Формула изобретения

Устройство задержки широтно-импульсного сигнала, содержащее входной формиП рователь, сдвигающие регистры с ключевыми схемами, интеграторы и схемы сравнения, элемент задержки в виде счетчика и схемы совпадения, собирательную схему и триггер, о т л к ч а ю ш е е с я тем, что, с целью повышения точности и величины задержки, вхс.w интеграторов соединены с источниками постоянного отрицательного и положительного напряжения через ключевые схемы, управляющие входы которых соединены с выходами соответственно первого и второго 4двигаюших регистров, входы которых связаны с вщц>.. дом входная о формирователя, причем вход первого - непосредственно, а второго через элемент задержки, выходы интеграторов подсоединены ко входам схем сравнения, выходы которых через собирательную схему подсоединены к одному входу

М триггера, второй вход которого подсоединен к источнику входного сигнала.

<96668

Составитель Т.БОгдйломм

Редактор Т,1цщ ори Твкред 11.у(лр дщщдова корректор Л.денискина

Заказ 2 00 Изд. М /Ц $ Тирам 902 Подлисвое

Ш1ЮП1И Госуларствеииого комитета Совета Министров СССР по делам изобретений и открытий

Москва, !ИОЗЕФ, Раушская иаб. ° 4

Филиал llllH "Патент, г. Ужгород, ул. Проектная, 4