Логическая ячейка

Иллюстрации

Показать всеРеферат

р) 497584

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Севе Советских

Социвлиетичвских

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 04.04.74 (21) 2010875/18-24 с присоединением заявки № (23) Приоритет (51) М. Кл. б 06f 7/38

Госуаврствениый комитет

Совете Министров СССР (53) УДК 681.3(088.8) по делом изобретеиий Опубликовано 30.12.75. Бюллетень ¹ 48 и открытий

Дата опубликования описания 18.03.76 (72) Автор изобретения

В. В. Авраменко

Ордена Ленина институт кибернетики АН Украинской ССР (71) Заявитель (54) ЛОГИ Ч ЕСКАЯ Я Ч ЕЙ КА

Изобретение относится к вычислительной технике-и предназначено для построения сумматоров ЦВМ.

Известны логические ячейки, содержащие нагрузочный транзистор, затвором соединенный с источником смещения, истоком — с выходом ячейки и со стоками первого и второго ключевых транзисторов, истоки которых соединены соответственно со стоками третьего и четвертого ключевых транзисторов, истоками соединенных с шиной нулевого потенциала.

Цель изобретения — сокращение в логической ячейке площади подложки, количества компонентов и количества внешних выводов при обеспечении работы,на общую магистраль, т. е. упрощение схемы.

Это достигается тем, что в предлагаемой ячейке между стоками третьего и четвертого ключевых транзисторов включен дополнительный ключевой транзистор, затвор третьего ключевого транзистора соединен с затвором второго ключевого транзистора, затворы первого, третьего, четвертого и дополнительного ключевых транзисторов соединены соответственно с четырьмя входами логической ячейки, подложки транзисторов соединены между собой и со стробирующим входом логической ячейки.

За счет соединения внутри ячейки затворов двух транзисторов (в противоположных плечах моста) достигается сокращение числа ее выводов. Применение в ячейке мостпкового включения МДП-транзистора, обеспечивающего в процессе функционирования ячейки

5 протекание через него тока то в одном, то в противоположном направлении, позволяет увеличить функциональные возможности ячейки и сократить площадь кристалла полупроводника.

10 При наличии запрещающего потенциала на стробирующем входе ни один из транзисторов не проводит и не шунтируется общая магистраль при объединении выходов нескольких элементов.

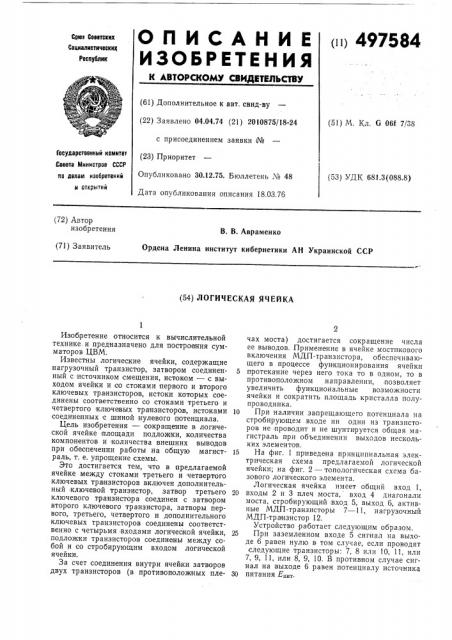

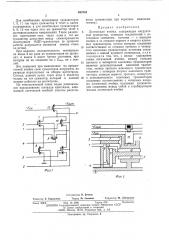

15 На фиг. 1 приведена принципиальная электрическая схема предлагаемой логической ячейки; на фиг. 2 — топологическая схема базового логического элемента.

Логическая ячейка имеет общий вход 1, 20 входы 2 и 3 плеч моста, вход 4 диагонали моста, стробирующий вход 5, выход 6, активные МДП-транзисторы 7 — 11, нагрузочный

МДП-тр а нзистор 12.

Устройство работает следующим образом.

25 При заземленном входе 5 сигнал на выходе 6 равен нулю в том случае, если проводят следующие транзисторы: 7, 8 или 10, 11, или

7, 9, 11, или 8, 9, 10. В противном случае сигнал на выходе 6 равен потенциалу источника

30 питания Е»,.

497584

Составитель П. Бочков

Редактор Е. Караулова Техред М. Семенов Корректор М. Лейзерман

Заказ 392/8 Изд. № 2086 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Для комбинации проводящих транзисторов

7, 9, 11 ток через транзистор 9 течет в одном направлении, а для комбинации транзисторов

8, 9, 10 ток через этот же транзистор течет в противоположном направлении. Такое различное протекание тока через один и тот же транзистор допустимо ввиду симметричности конструкции МДП-транзистора (в процессе работы допускается взаимная замена стока на исток).

При наличии положительного потенциала на входе 5 ни один из транзисторов не проводит, и выход 6 имеет третье состояние, при котором он не соединен ни с Е н„ни с землей.

Это позволяет при выполнении на предлагаемой ячейке схем сумматоров нагружать их разряды .параллельно на общую магистраль, Сигнал, равный нулю, через вход 5 подается только на тот сумматор,:который в данный момент работает,на магистраль.

На топологической схеме видно рациональное использование площади кристалла, занимаемой логической ячейкой (плотно расположены транзисторы при коротких межсоединениях).

Предмет изобретения

5 Логическая ячейка, содержащая нагрузочный транзистор, затвором соединенный с источником смещения, истоком — с выходом ячейки и со стоками первого и второго ключевых транзисторов, истоки которых соединены

10 соответственно со сто ками третьего и четвертого ключевых транзисторов, истоками соединенных с шиной нулевого потенциала, отли. ч а ю щ а я с я тем, что, с целью упрощения схемы логической ячейки, между стоками

15 третьего и четвертого ключевых транзисторов включен дополнительный ключевой транзистор, затвор третьего ключевого транзистора соединен с затво ром второго ключевого транзистора, затворы первого, третьего, четвертого

20 и дополнительного ключевых транзисторов соединены соответственно с четырьмя, входами логической ячейки, подложки транзисторов соединены между собой и стробирующим входом логической ячейки.