Устройство для преобразования постоянного напряжения в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (ц 492727

1 т"

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.05.73 (21) 1925815/26-21 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 30.12.75. Бюллетень № 48 (45) Дата опубликования описания 21.04.78 (51) М. Кл.2 Н 03К 13/20

G 06g 7/16

Государственный комитет

Совете Министров СССР ао делам изобретений и открытий (53) УДК 681.325(088.8) (72) Автор изобретения

В. С. Федак

Институт гидробиологии АН УССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПОСТОЯННОГО

НАПРЯЖЕНИЯ В КОД

Изобретение относится к аналого-цифровым устройствам автоматики и вычислительной техники и может быть использовано в арифметических блоках цифровых регуляторов, а также в устройствах сбора и первичной обработки информации электронно-цифровых вычислительных машин.

Известно устройство для преобразования постоянного напряжения в код, содержащее формирователь экспоненциальной развертки, своими выходами подключенный к первым входам двух схем сравнения, вторые входы которых подключены к входным клеммам устройства, а выходы — к входам соответствующих триггеров памяти результатов сравнения, своими выходами соединенных с первыми и вторыми входами схем И и ИЛИ, тактовый генератор, соединенный с первым входом сумматора число-импульсных кодов, своим выходом подключенного к цифровому аналогу RC-цепи, через вентиль, управляющий вход которого подключен к -рпггеру управления, нулевой вход последнего подключен к схеме И, а единичный — к шине «пуск».

Недостатком известного устройства является отсутствие возможности совмещения операции преобразования с операцией умножения входных напряжений.

Целью изобретения является совмещение операций преобразования и умножение входных напряжений.

Цель достигается пу-ем введения в устройство триггера блокировки, линии задержки и дополнительной схемы И. При этом выход схемы ИЛИ соединен с первым входом дополнительной схемы И, выход которой через линию задержки подключен к второму входу сумматора число-импульсных кодов и единичному входу триггера блокировки, единичный выход которого соединен с третьим входом

10 схемы И, а нулевой — с вторым входом дополнительной схемы И, третий вход которой подключен к выходу вентиля и входу сумматора число-импульсных кодов.

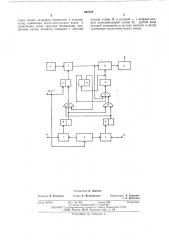

15 На чертеже представлена функциональная схема устройства для преобразования постоянного напряжения в код.

Устройство для преобразования постоянного напряжения в код содержит схему 1 срав20 нения, формирователь 2 "-кспоненцпальной развертки, триггер 3 управления, тактовый генератор 4, вентиль 5, цифровой аналог 6

RC-цепи, схему 7 сравнения, триггеры 8 и 9 памяти результатов сравнения, схему 10 И, 25 схему 11 ИЛИ, схему 12 И, триггер 13 блокировки, линию 14 задержки и сумматор 15 число-имп льсных кодов.

Преобразование постоянного напряжения во временной интервал производится в уст30 ройстве путем сравнения входного напряжения с напряжением формирователя экспонен497727 цпальной развертки, которое изменяется по закону:

U=Ee где Š— начальное напряжение на конденсаторе формирователя экспоненциальной развертки, t — время разряда, т — постоянная времени цепи разряда.

При Е= 1 временной интервал, пропорциональный входному напряжению, равен:

t= 1nU.

При заполнении временного интервала импульсами стабильной частоты число импульсов равно V=sylnU, где y — коэффициент, зависящий от частоты заполняющих импульсов.

lIp» умножении этого числа импульсов на

1 коэффициент Й = (т. е, при выборе

I нужной частоты заполнения) получается число-импульсный код, пропорциональный логарифму входного напряжения.

Для получения числа импульсов, пропорционального логарифму произведения напряжения, производят суммирование чисел импульсов, соответствующих сомножителям:

1Ч = А, + 7Ч; „ i — y k (in U, + Iп Ui „1) =

= lп (Ug Ul.+,1).

Полученная сумма преобразуется по закону У! =е-, что эквивалентно потенциированию.

У стройство работает следующим образом.

В исходном состоянии все триггеры устройства находятся в нулевом положении.

llри нажатии на кнопку «пуск» запускается формирователь 2 экспоненциальной развертки и напряжение с него поступает на схемы 1 и 7 сравнения, а триггер 8 управления ставится в единичное положение и единичным выходом открывает вентиль 5, через который импульсы с генератора 4 поступают на сумматор 15.

11ри достижении равенства напряжения развертки и меньшего из входных напряжений (U или Uz) срабатывает одна из схем сравнения 1 или 7 и устанавливает соответствующий ей триггер 8 или 9 в единичное состояние. Потенциал с единичного выхода этого триггера поступает на схему II ИЛИ. Выходной сигнал со схемы 11 дает разрешение на схему 12 И, на одном из входов которой уже есть разрешение с нулевого выхода триггера 13.

При поступлении очередного счетного импульса с вентиля 5 на схему 12 И последняя выдает сигнал, который через линию 14 задержки поступает на вход сумматора 15 и сдвигает его содержимое на один разряд, что эквивалентно умножению на 2. Импульс с линии 14 задержки поступает также на вход триггера 13 блокировки и устанавливает его в единичное состояние. Сигнал с единичного выхода триггера 13 дает разрешение на вход

32

СО

65 схемы 10 И, а сигнал с нулевого выхода— запрет па схему 12 И.

I IpH достижении равенства напряжения развертки большему из входных напряжений срабатывает соответствующая схема 1 или 7 сравнения, устанавливая соответствующий триггер 8 или 9 в единичное состояние. Сигнал совпадения единичных состояний триггеров 8 и 9 с выхода схемы 10 И поступает на нулевой вход триггера 3 управления и переводит его в нулевое состояние. При этом потенциал с единичного выхода триггера 3 поступает на вход вентиля 5 и запирает его.

llри этом прекращается подача счетных импульсов тактового генератора 4 на сумматор

15 число-импульсных кодов. Полученный в сумматоре код в виде последовательности импульсов поступает на цифровой аналог б

КС-цепи, выходной код которого будет пропорционален произведению напряжений U

И U2 °

В случае равенства входных напряжений триггеры 8 и 9 сработают одновременно и выдадут сигналы на схему 10 И и схему 11 ИЛИ. Сигнал с выхода схемы 11

ИЛИ при наличии счетного импульса через схему 12 И и линию 14 задержки поступает на сумматор 15 и производит сдвиг содержимого сумматора на один разряд. Зтот же сигнал с линии 14 задержки поступает на вход триггера 13, устанавливая его в единичное состояние. Сигнал с единичного выхода триггера 13 через схему 10 И возвращает триггер

3 в нулевое состояние. Ilотенциал с единичного выхода триггера 3 поступает на вентиль

5 и запирает его. 11ри этом прекращается подача счетных импульсов с генератора 4 на сумматор 15, а на выходе цифрового аналога

КС-цепи установится код, пропорциональный произведению напряжений U и Uq.

Предмет изобретения

Устройство для преобразования постоянного напряжения в код, содержащее формирователь экспоненциальной развертки, своими выходами подключенный к первым входам двух схем сравнения, вторые входы которых подключены к входным клеммам устройства, а выходы — к входам соответствующих триггеров памяти результатов сравнения, своими выходами соединенных с первыми и вторыми входами схем И и ИЛИ, тактовый генератор, соединенный с первым входом сумматора число-импульсных кодов, своим выходом подключенного к цифровому аналогу RC-цепи, через вентиль, управляющий вход которого подключен к триггеру управления, нулевой вход последнего подключен к схеме И, а единичный — к шине «пуск», отличающееся тем, что, с целью совмещения операций преобразования и умножения входных напряжений, в него введены триггер блокировки, линия задержки и дополнительная схема И, причем выход схемы ИЛИ соединен с первым входом дополнительной схемы И, выход которой

497727

Составитель Л. Дарьина

Тсхред Е. Митрофанова

Редактор В. Булдаков

Корректоры; P. Беркович и Л. Брахнина

Заказ 907/20

Подписное

Изд. гГ 309 Тираж 902 по делам изооретений и открытий

ЦНИИПИ Государственного комитета Совета Министров СССР

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 через линию задержки подключен к второму входу сумматора число-импульсных кодов и единичному входу триггера блокировки, единичный выход которого соединен с третьим входом схемы И, а нулевой — с вторым входом дополнительной схемы И, третий вход которой подключен к выходу вентиля и входу сумматора число-импульсных кодов.