Импульсный делитель частоты

Иллюстрации

Показать всеРеферат

@с с., . г -- я ,, склй би пйот"= (ii) 497734

О П

Союз Советских

Социалистических

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Республик

,61) Дополнительное к авт. свпд-ву 389629 (22) Заявлено 13.09.74 (21) 2059075/26-21 с присоединением заявки № (23) Приоритет

Опуоликовано 30.12.75. Бюллетень ¹ 48

Дата опубликования описания 29.03.76 (51) М. Кл. H ОЖ 23/00

Н 031 21/06

Государственный комитет

Совета Министров СССР по делам изобретений и открытий

1 (53) УДК 621.374.4 (088.8) (72) Авторы изобретения

И. 3. Белик, М. И. Грищенко, Т, В, Стахно и H. В. Якимович (71) Заявитель (54) ИМПУЛЬСНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЪ|

f---Ю

Изобретение относится к импульсной технике и может быть использовано в цифровых измерительных приборах и устройствах автоматики.

Известен импульсный делитель частоты по авт. св. № 389629.

Однако известный импульсный делитель частоты не обладает достаточной надежностью.

Целью изобретения является повышение надежности работы делителя частоты.

С этой целью в него введены триггер и дешифратор нулевого состояния, входы которого соединены с выходами накопительного счетчика, а выход — с нулевым входом триггера, единичный вход которого подключен к выходу устройства сравнения, а выход — к одному из входов логического элемента «ИЛИ».

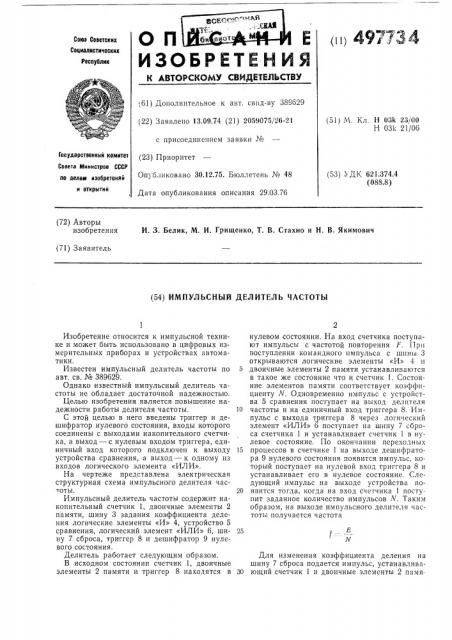

На чертеже представлена электрическая структурная схема импульсного делителя час оты.

Импульсный делитель частоты содержит накопительный счетчик 1, двоичные элементы 2 памяти, шину 3 задания коэффициента деления логические элементы «И» 4, устройство 5 сравнения, логический элемент «ИЛИ» 6, шину 7 сброса, триггер 8 и дешифратор 9 нулевого состояния.

Делитель работает следующим образом.

В исходном состоянии счетчик 1, двоичные элементы 2 памяти и триггер 8 находятся в

2 нулевом состоянии. На вход счетчика поступают импульсы с частотой повторения F. Прп поступлении командного импульса с шины 3 открываются логические элементы «И» 4 и

5 двоичные элементы 2 памяти устанавливаются в такое же состояние что и счетчик 1. Состояние элементов памяти соответствует коэффициенту N. Одновременно импульс с устройства 5 сравнения поступает на выход делителя

10 частоты и на единичный вход триггера 8. Импульс с выхода триггера 8 через логический элемент «ИЛИ» 6 поступает на шину 7 сороса счетчика 1 и устанавливает счетчик 1 в нулевое состояние. По окончании переходных

15 процессов в счетчике 1 на выходе дешифратора 9 нулевого состояния появится импульс, который поступает на нулевой вход триггера S u устанавливает его в нулевое состояние. Следующий импульс на выходе устройства по20 явится тогда, когда на вход счетчика 1 поступит заданное количество импульсов Л . Таким образом, на выходе импульсного делителя частоты получается частота

Для изменения коэффициента деления на шину 7 сброса подается импульс, устанавлива30 ющий счетчик 1 и двоичные элементы 2 памя.

497734

Составитель М. Аудринг

Техред Е. Митрофанова

Редактор В. Булдаков

Корректор E. Рожкова

Заказ 399/19 Изд. № 2119 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-З5, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ти в нуль. Новое значение коэффициента деления устанавливается аналогично.

Предмет изобретения

Импульсный делитель частоты по авт. св, № 389629, отличающийся тем, что, с целью 1товышения надежности era работе, в него введены триггер и дешифратор нулевого состояния, входы которого соединены с выходами накопительного счетчика, а выход — с нулевым входом триггера, единичный вход которого подключен к выходу устройства сравнения, а выход — к одному из входов логического элемента «ИЛИ».