Цифровой регулятор соотношения скоростей ведущего и приводного двигателей

Иллюстрации

Показать всеРеферат

СПИ гп) 498606

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. спид-ву (22) Заявлено 24.05.74 (21) 2027654/18-24 (51) М Кл е б 05D 13/00 с присоединением заявки №

Государственный комитет

Совета Цииистров СССР т"т дним изобретений и Отнрытин (23) Приоритет

Опубликовано 05.01.76. Бюллетень № 1

Дата опублпковапия описания 18.03.76 (53) УДК 62-50(088.8) (72) Авторы изобретения

М. П. Козин и Ф. Н. Рассказов (71) Заявитель

Куйбышевский политехнический институт им. В. В. Куйбышева (54) ЦИФРОВОЙ РЕГУЛЯТОР СООТНОШЕНИЯ СКОРОСТЕЙ

ВЕДУЩЕГО И ПРИВОДНОГО ДВИГАТЕЛЕЙ

Изобретение может быть использовано в металлургической, текстильной, бумагоделательной и других отраслях промышленности.

Известен цифровой регулятор соотношения скоростей двигателей, содержащий датчик импульсов ведущего и приводного двигателей и регулятор приводного двигателя.

Малое быстродействие известного цифрового регулятора определяется промежутком времени подсчета импульсов счетчиком.

С целью повышения быстродействия в регуляторе использовано аналоговое регулирование в совокупности с цифровым. Однако комбинация цифрового и аналогового регулирования не всегда позволяет точно поддерживать соотношение скоростей двигателей (например, при быстром изменении программы скорости ведущего двигателя) .

Целью изобретения является повышение быстродействия и точности цифрового регулятора соотношения скоростей.

Эта цель достигается тем, что в цифровой регулятор введены частотный компаратор и последовательно соединенные управляемый делитель частоты, фазовый дискриминатор и фильтр, выход которого подключен ко входу регулятора приводного двигателя. Второй вход фазового дискриминатора подключен к выходу частотного компаратора, первый вход которого подключен к выходу датчика импульсов ведущего двигателя и входу управляемого делителя частоты, а второй — к выходу датчика импульсов приводного двигателя.

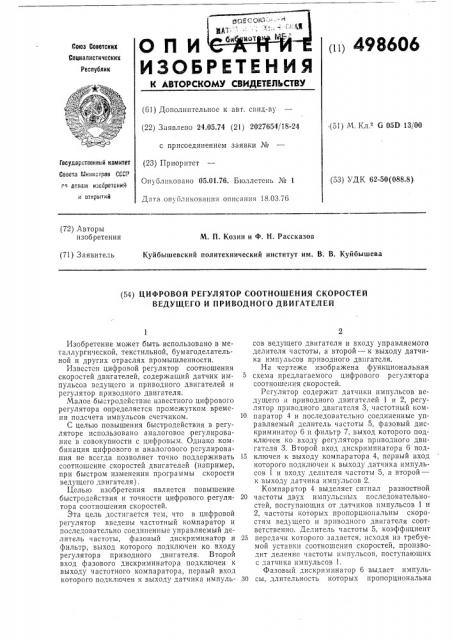

На чертеже изображена функциональная

5 схема предлагаемого цифрового регулятора соотношения скоростей.

Регулятор содержит датчики импульсов ведущего и приводного двигателей 1 и 2, регулятор приводного двигателя 3, частотный ком10 паратор 4 и последовательно соединенные управляемый делитель частоты 5, фазовый дискриминатор 6 и фильтр 7, выход которого подключен ко входу регулятора приводного двигателя 3. Второй вход дискриминатора G под15 ключен к выходу компаратора 4, первый вход которого подключен к выходу датчика импульсов 1 и входу делителя частоты 5, а второй— к выходу датчика импульсов 2.

Компаратор 4 выделяет сигнал разностной

20 частоты двух импульсных последовательностей, поступающих от датчиков импульсов 1 и

2, частоты l

25 передачи кото рого задается, исходя из требуемой уставки соотношения скоростей, производит деление частоты импульсов, поступающих с датчика импульсов 1.

Фазовый дискриминатор 6 выдает импульЗО сы, длительность которых пропорциональна

498606

Составитель Г. Романченко

Техред T. Курилко Корректор М. Лейзерман

Редактор Л. Утехина

Заказ 435/9 Изд. № 182 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, >К-35, Раушская наб., д. 4, 5

Типография, пр. Сапунова, 2 разности фаз импульсных последовательностей, поступающих с выходов компаратора 4 и делителя частоты 5.

Фильтр 7 выдает аналоговое напряжение, пропорциональное длительности импульсов, поступающих с дискриминатора 6, которое подается на вход аналогового регулятора 3. В процессе функционирования регулятора частоты импульсных последовательностей, поступающих с делителя частоты 5 и компаратора 4 10 на входы дискриминатора 4, равчы между собой. Последовательности отличаются на фазе.

Равенство частот указанных импульсных последовательностей свидетельствует о равенстве действительного соотношения скоростей 15 заданному. Задание на соотношение скоростей двигателей устанавливается коэффициентом передачи делителя частоты 5.

Быстродействие и точность предлагаемого цифрового регулятора определяется периодом 20 разностной частоты датчиков импульсов ведущего и приводного двигателей 1 и 2.

Период указанной разностной частоты намного меньше промежутка времени подсчета импульсов счетчиком в известном цифровом 25 регуляторе, поэтому быстродействие и точность предлагаемого регулятора выше, чем точность и быс цродействие известного регулятора.

Схема предлагаемого цифрового регулятора более проста, чем схема известного, так как он не требует применения аналогового контура регулирования.

Формула изобретения

Цифровой регулятор соотношения скоростей ведущего и приводного двигателей, содержащий датчики импульсов ведущего и приводного двигателей и регулятор приводного двигателя, отличающийся тем, что, с целью повышения быстродействия и точности работы регулятора, в него введены частотный компаратор и последовательно соединенные управляемый делитель частоты, фазовый дискриминатор и фильтр, выход которого подключен ко входу регулятора приводного двигателя, а второй вход фазового дискриминатора подключен к выходу частотного компаратора, первый вход которого подключен к выходу датчика импульсов ведущего двигателя и входу управляемого делителя частоты, а второй — к выходу датчика импульсов приводного двигателя.