Стабилизатор постоянного напряжения с защитой

Иллюстрации

Показать всеРеферат

и1 498616

ОП ИСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено 20.05.74 (21) 2027163/24-7 (51) М. Кл. G 05F 1/58 с присоединснисм заявки №

Государственный комитет

Совета Министров СССР (23) Приоритет

Опуоликовано 05.01.76. Бтоллетень № 1

Дата опубликования описания 18.03.76 (53) УДК 621.316.722.1 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. С. Щербаков и К. К, Огарков (71) Заявитель Тульская дистанция сигнализации и связи Московской железной дороги (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

С ЗАЩИТОЙ

Изобретение относится к вторичным источникам питания.

Известны стабилизаторы постоянного напряжения с защитой от перегрузок и коротких замыканий, содержащие усилитель постоянного тока, вход которого соединен с о рганом сравнения, включающим источник опорного напряжения, а выходной каскад на транзисторе подключен к управляющему входу регулирующего транзистора с теплоотводом и резистивным датчиком тока в эмиттерной цепи, соединенной с источником питающего напряжения.

Однако для известных стабилизаторов характерна сложная схема, отсутствие ограничения мощности, рассеиваемой на регулирующем транзисторе при перенапряжении на входе, а также нестабильный порог срабатывания защиты и низкая надежность.

Цель предлагаемого изобретения — ограничение мощности, рассеиваемой на регулирующем транзисторе при перенапряжении на входе, обеспечение стабильного по рога срабатывания защиты, повышение надежности.

Указанная цель достигается тем, что в стабилизатор постоянного напряжения с защитой дополнительно введены источник опорного напряжения и стабилитрон. Дополнительный источник опорного напряжения подключен между входной шиной и эмиттером транзистора выходного каскада усилителя постоянного тока, а стабилитрон — между базой этого транзистора и выходной шиной со стороны регулирующего транзистора.

B качестве дополнительного источника onoipного напряжения используется параметрический стабилизатор на полупроводниковых диодах, из которых один или несколько установлены на теплоотводе регулирующего транзистора.

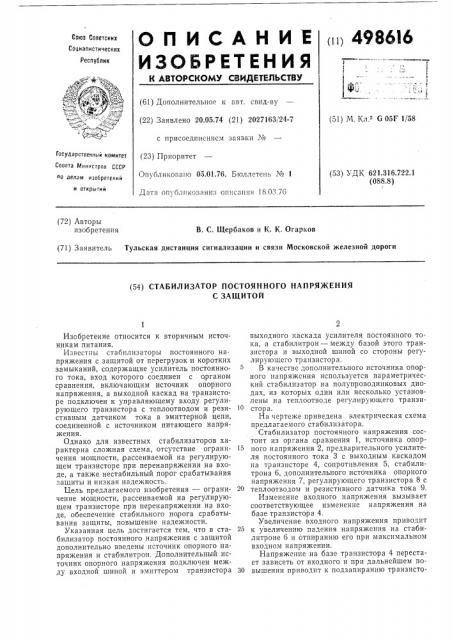

На чертеже приведена электрическая схема предлагаемого стабилизатора.

Стабилизатор постоянного напряжения состоит из органа сравнения 1, источника опорного напряжения 2, предварительного усилителя постоянного тока 3 с выходным каскадом на транзисторе 4, сопротивления 5, стабилитрона 6, дополнительного источника опорного напряжения 7, регулирующего транзистора 8 с теплоотводом и резистивного датчика тока 9.

Изменение входного напряжения вызывает соответствующее изменение напряжения на базе транзистора 4.

Увеличение входного напряжения приводит

25 к увеличению падения напряжения на стабилитроне 6 и отпиранию его при максимальном входном напряжении.

Напряжение на базе транзистора 4 перестает зависеть от входного и при дальнейшем по30 вышении приводит к подзапиранпю транзисто498616

Предмет изобретения

2. Стабилизатор по п. 1, отличающийся

30 тем, что, с целью улучшения термостабильности порога срабатывания защиты, в качестве дополнительного источника опорного напряжения использован параметрический стабилизатор на полупроводниковых диодах, часть ко35 торых устанавливается на теплоотводе регулир ую щего тр анз истор а.

Составитель Ю. Дычко

Техред Т. Курилко

Корректор М. Лейзерман

Редактор Е. Меньшова

Заказ 435/18 Изд. № 182 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ра 4 из-за роста потенциала его эмитте ра, Ток транзистора 8 уменьшается, что приводит к дальнейшему запиранию транзистора 4.

Процесс происходит лавинообразно и заканчивается запиранием транзистора 8. При увеличении погрузочного тока растет падение напряжения на 1резистивном датчике тока 9 и при определенном его значении происходит насыщение транзистора 4, а резистивный датчик тока 9, транзистор 8 и дополнительный источник опорного напряжения образуют параметрический стабилизатор тока.

Дальнейшее уменьшение выходного сопротивления приводит к падению выходного напряжения, а следовательно, к повышению пап ряжения на стабилитроне б и увеличению мощности, рассеиваемой на транзисторе 8 до момента отпирания стабилитрона 6. Затем происходит лавинообразный процесс запирания, аналогичный процессу при перенапряжении на входе.

Наличие режима стабилизации выходного тока значительно повышает устойчивость защиты стабилизатора к ложным срабатываниям при импульсных перегрузках, а запирание стабилизатора имеет место при одном и том же значении падения напряжения на транзисторе 8, близком к напряжению стабилизации стабилитрона 6.

В качестве дополнительного источника опорного напряжения используют параметрический стабилизатор на полупроводниковых диодах.

В этом случае имеет место компенсация температурных изменений напряжения насыщения пранзистора 4 и эмиттерного перехода транзистора 8.

Установка полупроводниковых диодов на теплоотводе транзистора 8 улучшает термостабильность устройства.

1. Стабилизатор постоянного напряжения с защитой от перегрузок и коротких замыканий, 10 содержащий усилитель постоянного тока, вход которого соединен с органом сравнения, включающим источник опорного напряжения, а выходной каскад на транзисторе подключен к управляющему входу регулирующего транзи15 стора с теплоотводом и резистивным датчиком тока в эмиттерной цепи, соединенной с источником питающего напряжения, о т л и ч а юшийся тем, что, с целью ограничения мощности, рассеиваемой на регулирующем транзи20 сторе, и обеспечения стабильного порога срабатывания защиты, между входной шиной стабилизатора до резистивного датчика тока и эмиттером транзистора выходного каскада усилителя постоянного тока включен дополни25 тельный источник опорного напряжения, а между базой этого транзистора и выходной шиной стабилизатора — стабилитрон.