Устройство для контроля цифровых узлов

Иллюстрации

Показать всеРеферат

00 498619

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.07.74 (21) 2040388/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.01.76. Бюллетень № 1

Дата опубликования описания 22.03.76 (51) М, Кл. G 06F 11/00

G 05В 23/02

Государственный комитет

Совета Министров СССР (53) УДК 681.325.65:621. .382 (088.8) ло делам изобретений и открытий (72) Авторы изобретения А. И. Дубовик, М. Г. Дубров, Г. В. Лисовская и Р. Б. Вайс (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ

Изобретение относится к области вычислительнои техники.

Известны устройства для контроля цифровых узлов, содержащие блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления. первый выход блока ввода соединен со входом олока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внешними контактами контролируемого узла. Второй выход блока ввода соединен со входом олока управления, выходы которого подключены соответственно к управляющим входам блока ввода, блока памяти и блока индикации, соединенного входом с выходом блока ср авнения.

Однако такое устройство сложно, так как в нем помимо блока входных и эталонных сигналов использован блок контролируемых выходов, выполненный в виде магазинного ЗУ переменного объема. Кроме того, в устройстве отсутствует контроль правильности подачи сигналов, подаваемых на входные контакты проверяемого узла.

Целью изобретения является упрощение устройства и повышение достоверности его работы.

Поставленная цель достигается тем, что в предложенное устройство введен регистр настройки, соединенный входом с первым выходом блока ввода, управляющим входом — с выходом блока управления, а выходом — со вторым входом коммутатора. Выход блока памяти подключен к первому входу блока сравнения, второй вход которого соединен с выходом коммутатора.

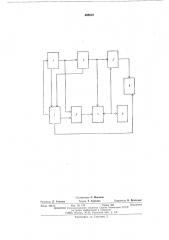

Схема устройства представлена на чертеже.

Устройство содержит блок 1 ввода, блок 2 памяти, регистр настройки 3, коммутатор 4, 10 блок 5 сравнения, блок 6 индикации и блок 7 управления.

Блок ввода 1 предназначен для ввода с перфоленты тестовой информации, информации о входных (выходных) контактах и командной информации.

Блок 2 памяти предназначен для хранения и выдачи тестовой информации.

Регистр настройки 3, разрядность которого равна числу внешних контактов, служит для управления коммутатором 4.

Коммутатор 4 осуществляет передачу сигналов на входы проверяемого узла 8.

Блок 5 сравнения предназначен для сравнения кодов эталонов и стимулов с сигналами

25 на внешних контактах проверяемого узла.

Блок 6 индикации предназначен для индикации результатов контроля и при несоответствии кодов индикации номера элементарного теста и номера контакта, иа котором обнару30 жено несравнение.

Блок 7 управления организует работу всех блоков устройства, т. е. управляет записью информации из блока 1 ввода в блок 2 памяти и регистр настройки 3, управляет работой блока 6 индикации и осуществляет управление однократным и циклическим режимами работы.

Контроль проверяемого узла осуществляется с помощью тестов, состоящих из последовательности элементарных тестов, разрядность которых равна числу внешних контактов проверяемого узла.

Каждый элементарный тест включает в себя стимулы и эталоны. Стимулы — совокупность сигналов, одновременно подаваемых на входные контакты, эталоны — совокупность сигналов, которые должны появиться на выходах исправного узла при подаче на его входы стимулов.

Устройство работает следующим образом.

Командная информация из блока 1 ввода поступает в блок управления и включает следующие команды «Начало», «Запись 1», «Запись 2», «Проверка» и «Конец».

По команде «Начало», все блоки устройства устанавливаются в исходное состояние. По команде «Запись 1» в регистр настройки 3 записывается информация о входных контактах проверяемого узла. По команде «Запись 2» тестовая информация записывается в блок 2 памяти. По команде «Проверка» начинается считывание информации из блока 2. Очередной элементарный тест поступает на первые входы коммутатора 4, который выделяет стимулы из элементарного теста и подает их на входы проверяемого узла. Работой коммутатора 4 управляет регистр настройки 3, в котором хранится информация о входных контактах проверяемого узла, Одновременно элементарный тест поступает и на первые входы блока 5 сравнения. Стимулы, выделенные коммутатором из элементарного теста, поступают на входы проверяемого узла, а затем вместе с сигналом последнего поступают на вторые входы блока 5 сравнения.

В однократном режиме работы элементарные тесты на вход проверяемого узла подаются однократно, и по команде «Конец» на блоке индикации фиксируется результат коптрсля.

В случае несравнения каких-либо сигналов в блоке индикации отражается номер элементарного теста, в котором обнаружено несоответствие, и номер контакта, на котором произошло несравнение.

В циклическом режиме работы любая группа элементарных тестов циклически подается

1О на входы проверяемого узла, что позволяет проследить, например, с помощью осциллографа, прохождение сигналов внутри проверяемого узла и определить место неисправности.

Таким образом, в блоке сравнения не толь15 ко сравниваются коды эталонов с кодами реакции, но в каждом элементарном тесте проверяется правильность подачи стимулов на входы проверяемого узла. В результате повышается достоверность контроля, что особенно важно для проверки узлов, имеющих много внешних контактов и содержащих сложные коммутаторы.

Предмет изобретения

Устройство для контроля цифровых узлов, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход блока вво30 да соединен со входом блока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внешними контактами контролируемого узла, второй выход блока ввода соединен со входом блока уп35 равления, выходы которого подключены соответственно к управляющим входам блока ввода, блока памяти и блока индикации, соединенного входом с выходом блока сравнения, отличающееся тем, что, с целью упроще40 ния и повышения достоверности работы устройства, в него введен регистр настройки, соединенный входом с первым выходом блока ввода, управляющим входом — с выходом блока управления, выходом — со вторым вхо45 дом коммутатора; выход блока памяти подключен к первому входу блока сравнения, второй вход которого соединен с выходом коммутатора.

498619

Составитель А. )Керенов

Техред Т, Курилко

Редактор Л. Утехина

Корректор В. Брыксина

Заказ 423(15 Изд. Ж 179 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений п открытий

113035, Москва, )K-35, Раушская паб., д. 4/5

Типография, нр Сапунова, 2