Запоминающее устойство

Иллюстрации

Показать всеРеферат

Й б Р с о ит 5» н ф

1 ..

@ тбнтно-теах инцеста бтеблиотет,а М

ИСА (ii) 498648

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 19.04.74 (21) 2016730/18-24 с присоединением заявки Ме (23) Приоритет

Опубликовано 05.01.76. Бюллетень М 1

Дата опубликования описания 30.03.76 (51) М Кл 2 G 11С 11/34

Государственный комитет

Совета Министров СССР (53) УДК 681.326.33 (088.8) по делам изобретений н открытий (72) Автор изобретения

В. А. Авдеев

Таганрогский радиотехнический институт (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в устройствах памяти для хранения значений подыитегральной функции параллельных цифровых интегрирующих машин, сопряженных с

ЦВМ общего назначения.

Известны устройства, содержащие основные регистры, выполненные на триггерах, соединенных последовательно через вентили записи, собирательные схемы, дешифратор адреса и вспомогательный регистр; причем входы вентилей записи четных разрядов оснозных регистров соединены с первой шиной тактовых импульсов, а входы вентилей записи нечетных разрядов — со второй шиной тактовых импульсов.

Недостатком известных устройств являются значительные затраты времени при обмене числовыми данными цифровой интегрирующей машины, использующей известную память, с

ЦВМ, так KBK ввод (вывод) начальных значений подынтегральной функции в основные регистры осуществляется последовательным кодом, Целью изобретения является повышение быстродействия ЗУ.

Поставленная цель достигается за счет того, что предложенное устройство содержит дополнительные вентили записи нуля и единицы и вентили считывания единицы для каждого нечетного триггера основных регистров. . Нулевой выход каждого триггера вспомогательного регистра соединен с одним из входов дополнительного вентиля записи нуля соот.

5 ветствующего нечетного триггера каждого основного регистра, а единичный — с одним из входов дополнительного вентиля записи единицы соответствующего нечетного триггера каждого основного регистра. Другие входь1

10 дополнительных вентилей записи нуля и единицы и один из входов вентиля считывания каждого нечетного триггера основного регистра подключены к соответствующему выходу дешифратора адреса. Другие входы вентилей

15 считывания соединены с единичным выходом нечетного триггера основного регистра, а выходы вентилей считывания каждого соответствующего нечетного триггера основных регистров подключены через собирательную схему

20 к единичному входу соответствующего триггера вспомогательного регистра. Выходы дополнительных вентилей записи нуля и единицы подключены соответственно к нулевому и единичному входам нечетных триггеров основных

25 регистров.

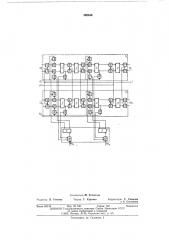

Схема ЗУ представлена на чертеже.

ЗУ состоит из основных регистров 1> — 1„и вспомогательного реиистра 2.

Основные регистры выполнены на тригге30 рах 3, соединенных последовательно через

498648

15 вентили записи нуля 4 и единицы 5. Другие входы вентилей записи четных разрядов основных регистров соединены с первой шиной

6 тактовых импульсов, а другие входы вентилей записи нечетных разрядов — со второй шиной 7 тактовых импульсов.

Нулевой выход каждого триггера 3 регистра

2 соединен с одним из входов дополнительного вентиля записи нуля 8 соответствующего нечетного триггера каждого основного регистра, а единичный выход каждого триггера регистра 2 —" одним из входов вентиля записи единицы 9 соответствующего нечетного триггера каждого регистра 1. Другие входы вентилей записи нуля и единицы 8 и 9 и один из входов вентиля считывания 10 каждого нечетного триггера регистра 1 соответственно подключены к одному из выходов 11,— 11„дешифратора адреса. Другие входы вентилей считывания 10 соответственно соединены с единичными выходами нечетных триггеров регистров 1, а выходы вентилей считывания

10 каждого нечетного триггера этих регистров подключены через собирательную схему 12 к единичному входу соответствующего триггера регистра 2. Выходы вентилей записи нуля 4 и

8 и вентилей единицы 5 и 9 подключены через собирательные схемы 13 соответственно к нулевым и единичным входам триггеров регистров 1. Входы 14 — 14>, используются для занесения числа из ЦВМ, а входы 15 — 15„— для подключения соответствующих выходов интеграторов цифровой интегрирующей машины.

Кроме того, каждый выход 16 — 16 соединен со входом соответствующего интегратора. Для вывода результатов решения интеграторов в память ЦВМ используются единичные выходы триггеров регистра 2 (на чертеже не показаны).

Предложенное ЗУ работает в двух режимах: в режиме решения цифровой интегрирующей машины (ЦИМ) и в режиме обмена информацией ЦИМ с ЦВМ или внешними устройствами.

В первом режиме основные регистры используются в качестве параллельно-последовательной памяти цифровой интегрирующей машины, т. е. в каждом основном регистре соответствующего интегратора информация циркулирует последовательно, а во всех интеграторах информация обрабатывается одновременно (параллельно).

С помощью первой и второй серий тактовых импульсов, поступающих соответственно на шины 6 и 7, осуществляется сдвиг информации в регистрах, т. е. выполняется ее цирку20

55 ляция в каждом интеграторе ЦИМ. Причем в двухтактных основных сдвигающих регистрах промежуточное хранение информации осуществляется в четных триггерах, а нечетные триггеры являются основными.

Во втором режиме записываемое число из

ЦВМ по входам 14 — 14>, заносится во вспомогательный регистр. Разрешение на запись числа в основной регистр выполняет дешифратор адреса сигналом на одной из выходных шин 11> — 11„. Аналогично выполняется считывание числа из определенного основного регистра во вспомогательный регистр, из которого затем число передается в память ЦВМ или во внешнее устройство.

Предмет изобретения

Запоминающее устройство, содержащее основные регистры, выполненные на триггерах, соединенных последовательно через вентили записи, собирательные схемы, дешифратор адреса и вспомогательный регистр, причем входы вентилей записи четных разрядов основных регистров соединены с первой шиной тактовых импульсов, а входы вентилей записи нечетных разрядов — со второй шиной тактовых импульсов, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит дополнительные вентили записи нуля и единицы и вентили считывания единицы для каждого нечетного триггера основных регистров; причем нулевой выход каждого триггера вспомогательного регистра соединен с одним из входов дополнительного вентиля записи нуля соответствующего нечетного триггера каждого основного регистра, а единичный — с одним из входов дополнительного вентиля записи единицы соответствующего нечетного триггера каждого основного регистра; другие входы дополнительных вентилей записи нуля и единицы и один из входов вентиля считывания каждого нечетного триггера основного регистра подключен к соответствующему выходу дешифратора адреса; другие входы вентилей считывания соединены с единичным выходом каждого нечетного триггера основного регистра, а выходы вентилей считывания каждого соответствующего нечетного триггера основных регистров подключены через собирательную схему к единичному входу соответствующего триггера вспомогательного регистра; выходы дополнительных вентилей записи нуля и единицы подключены соответственно к нулевому и единичному входам нечетных триггеров основных регистров.

Редактор Л. Утехина

Составитель Ю. Розенталь

Техред Т. Курилко

Кор ректоры: Е. Рожкова и А. Степанова

Заказ 425/16 Изд. № 180 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4,5

Типография, пр, Сапунова, 2