Устройство управляемой задержки сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

И8712

Союз Советских

Социалистических

Реслуолил (61) Дополнительное к авт. свид-ву (22) Заявлено 28.06.74 (21) 2039014/18-24 с присоединением заявки Ке (51) М. Кл.2 Н ОЗН 7/32

Совета Министров СССР ло делам изобретений и открытий

Опубликовано 05.01.76, Бюллетень Ме 1

Дата опубликования описания 07.04.76 (53) УДК 681.3(088.8) (72) Автор изобретения

Г, А. Брякалов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЯЕМОЙ ЗАДЕРЖКИ

СИГНАЛОВ

Государственный комитет (23) Приоритет

Изобретение относится к области автоматики и вычислительной техники.

Известны устройства для управляемой задержки сигнала, содержащие программный блок, соединенный с регистром, линию задержки с сосредоточенными параметрами на LCзвеньях и шину входных сигналов.

В таких устройствах значения индуктивности или емкости звена линии задержки могут изменяться в зависимости от сигналов, поступающих из программного блока.

Предложенное устройство отличается от известных тем, что в него введены дешифратор, входы которого подключены к выходам регистра, и элементы «И», один вход каждого из которых подключен к соответствующему выходу дешифратора, а другой — к общей шине входных сигналов. Выходы схем «И» соединены с соответствующими входами линии задержки.

Это позволяет, не меняя значений индуктивности или емкости звена линии задержки, варьировать лишь числом звеньев, включенных в работу, что расширяет класс решаемых задач и повышает точность работы устройства.

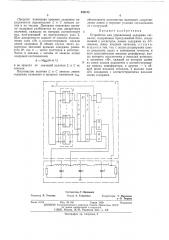

Блок-схема устройства приведена на чертеже.

Устройство содержит линию задержки 1 на

LC-звеньях. В качестве индуктивных 2 и емкостных 3 элементов звена линии использованы постоянные индуктивности и емкости. Блок управления 4 содержит программный блок 5, п-разрядный триггерный регистр 6, дешифра5 тор 7, схемы «И» 8 и общую шину входных сигналов 9, Время задержки сигнала в устройстве определяется по формуле:

1„„= — m PLC, где t»> — необходимое время задержки;

L и С вЂ” величины индуктивности и емкости звена линии задержки;

m — число звеньев линии.

15 Код, соответствующий определенному времени задержки, подается из программного блока 5 на триггеры п-разрядного регистра 6 и устанавливает их в единичное состояние. Дешифратор 7 преобразует код слова, находящий20 ся в регистре, в управляющий сигнал на одном из своих выходов. Управляющий сигнал подается на один из входов соответствующей схемы «И», на другой вход которой с общей шины поступает входной сигнал устройства.

25 Таким образом, в зависимости от кода, поступающего из программного блока, входной сигнал устройства подается в различные точки линии задержки, вследствие чего меняется число m работающих звеньев линии и время

30 задержки входного сигнала.

498712

Составитель Г. Брякалов

Техред 3. Тараненко

Редактор Л. Утехина

Корректоры: Т. Миронова и О. Тюрина

Заказ 411/5 Изд. № 165 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Пределы изменения времени задержки определяются параметрами L и С звеньев линии и их числом, Диапазон изменения времени задержки разбивается на ряд дискретных значений, каждому из которых соответствует код, поступающий из программного узла 5.

Шаг дискретности зависит от способа подключения схем «И» к соответствующим входам линии задержки. В общем случае число дискретных значений времени задержки равняется 2", где п. — число триггеров в регистре.

Число а связано с числом т звеньев линии задержки соотношением

n = log,(ò+1) и не зависит от значений величин L и С ее звеньев.

Постоянство величин L и С звеньев линии задержки позволяет в процессе изменения t,„ обеспечивать постоянство волнового сопротивления линии и хорошие условия согласования ее с нагрузкой.

5 Предмет изобретения

Устройство для управляемой задержки сигналов, содержащее программный блок, соединенный с регистром, линию задержки на LCзвеньях, шину входных сигналов, о т л и ч а10 ю щ е е с я тем, что, с целью расширения класса решаемых задач и повышения точности, в него дополнительно введены дешифратор, входы которого подключены к выходам регистра, и элементы «И», каждый из которых одним

15 из своих входов подключен к соответствующему выходу дешифратора, а другим — к общей шине входных сигналов, а выходы схем

«И» соединены с соответствующими входами линии задержки.