Адресный дешифратор

Иллюстрации

Показать всеРеферат

О П И C А Н И Е- (») 498737

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.03.74 (21) 2007094/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 05.01.76. Бюллетень ¹ 1

Дата опубликования описания 23.03.76 (51) М. Кл.2 Н ОЗК 13/25

Государственный Комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325.63 (088.8) (72) Автор изобретения

М. А. Исаков (71) Заявитель (54) АДРЕСНЫЙ ДЕШИФРАТОР

Изобретение относится к вычислительной технике, может использоваться в оперативном запоминающем устройстве ЭВМ малой емкости.

Известен адресный дешифратор, содержащий числовые линейки, одни концы которых соединены с горизонтальными шинами координатной сетки, а другие — с анодами и катодами соединенных попарно диодов, катоды и аноды которых соответственно подключены к первым и вторым вертикальным шинам координатной сетки, нижние и верхние ключи на транзисторах разных типов проводимости, в которых коллекторы транзисторов нижних ключей соединены с первыми вертикальными шинами координатной сетки, а эмиттеры подключены к общей шине.

Однако большое количество ключей и относящихся к ним схем снижает надежность устройства.

Цель изобретения — повышение надежности устройства — достигается тем, что в предлагаемом дешифраторе дополнительно установлены транзисторы и стабилизаторы тока, причем коллекторы дополнительных транзисторов соединены со вторыми вертикальными шинами координатной сетки, базы подключены к коллекторам транзисторов нижних ключей, а эмиттеры — к одному концу первого стабилизатора тока, коллекторы транзисторов верхних ключей через конденсаторы и другие диоды соединены соответственно с горизонтальными шинами координатной сетки и другим концом первого стабилизатора, а эмиттеры транзисторов верхних ключей через второй стабилизатор подключены к положительному полюсу источника питания.

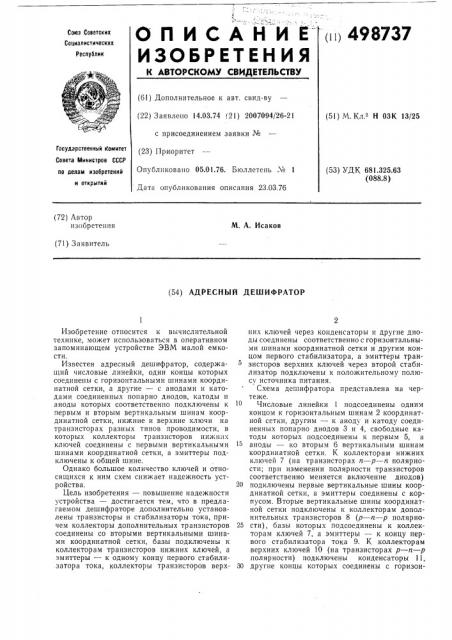

Схема дешифратора представлена на чертеже.

Числовые линейки 1 подсоединены одним концом к горизонтальным шинам 2 координатной сетки, другим — к аноду и катоду соединенных попарно диодов 3 и 4, свободные катоды которых подсоединены к первым 5, а

15 аноды — ко вторым 6 вертикальным шинам координатной сетки. К коллекторам нижних ключей 7 (на транзисторах и — р — и полярности; при изменении полярности транзисторов соответственно меняется включение диодов)

20 подключены первые вертикальные шины координатной сетки, а эмиттеры соединены с корпусом. Вторые вертикальные шины координатной сетки подключены к коллекторам дополнительных транзисторов 8 (р — и — р полярно25 сти), базы которых подсоединены к коллекторам ключей 7, а эмиттеры — к концу первого стабилизатора тока 9. К коллекторам верхних ключей 10 (на транзисторах р — и — р полярности) подключены конденсаторы 11, 30 другие концы которых соединены с горизон498737

Предмет изобретения

"Ест

1g

ЦНИИПИ Заказ 431!15 Изд. № 164 Тираж 1029 Подписное

Типография, пр. Сапунова, 2 тальными шинами координатной сетки. Цепи разряда конденсаторов образованы первым стабилизатором тока 9, диодами 12 с анодами, подключенными к коллекторам верхних ключей, и транзисторами 8. Эмиттеры верхних ключей через второй стабилизатор тока

13 соединены с источником питания.

Устройство работает следующим образом.

Потенциалами логических схем адреса открывается один из ключей 7 и один из ключей 10.

В момент считывания сигналом 14 открывается стабилизатор 13, и источник питания через открытый ключ 10, конденсатор 11, выбранную линейку 1, диод 3, открытый ключ 7 создает ток прямой полярности (15 — верхняя полуволна), ограничиваемый на нужном уровне стабилизатором 13. При этом заряжается конденсатор 11 выбранной координатной линии. Б момент записи сигнал 16 открывает стабил затор 9 и транзистор 8 открытого ключа 7, и через диод 12, стабилизатор 9, открытый ключ 8, диод 4, выбранную линейку 1 конденсатор 11 разряжается, создавая в цепи ток обратной полярности (15 — нижняя полуволна), ограничиваемый на нужном уровне стабилизатором 9.

Дешифратор использует оди н источник питания, что позволяет, в частности, связать верхние ключи с логическими схемами без трансформаторов.

Адресный дешифратор, содержащий числовые линейки, одни концы которых соединены с горизонтальными шинами координатной сетки, а другие — с анодами и катодами соединенных попарно диодов, катоды и аноды которых соответственно подключены к первым и вторым вертикальным шинам координатной сетки, нижние и верхние ключи на транзисторах разных типов проводимости, в которых коллекторы транзисторов нижних ключей соединены с первыми вертикальными шинами координатной сетки, а эмиттеры подключены к общей шине, отличающийся тем, что, с целью повышения надежности, в нем дополнительно установлены транзисторы и стабилизаторы тока, причем коллекторы дополнительных транзисторов соединены со вторыми вертикальными шинами координатной сетки, базы подключены к коллекторам транзисторов нижних ключей, а эмиттеры — к одному концу первого стабилизатора тока, коллекторы транзисторов верхних ключей через конденсаторы и другие диоды соединены соответственно с горизонтальными шинами координатной сетки и другим концом первого стабилизатора, а эмиттеры транзисторов верхних кючей через второй стабилизатор подключены к поло30 жительному полюсу источника питания.