Делитель частоты

Иллюстрации

Показать всеРеферат

0 1 499674

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву 401005 (22) Заявлено 27.11.74 (21) 2078521/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 15.01.76. Бюллетень № 2

Дата опубликования описания 29.03.76 (51) «1, Кл,- вН ОЗК 23/00

Государственный комитет

Совета Министров СССР (53) УДК 621,374.4 (088.8) ло делам изобретений и открытий (72) Автор изобретения

В. М. Карпенко (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к радиотехнике, может использоваться в цифровых синтезаторах частоты, применяемых в радиолокации и радиосвязи.

Известен делитель частоты по основному авт. св. № 401005.

Однако, в известном устройстве скважность выходных импульсов при нечетных коэффициентах деления не равна двум, что имеет значение при малых коэффициентах деления.

Целью изобретения является поддержание скважности выходных импульсов, равной двум при любом коэффициенте деления.

Это достигается тем, что в предлагаемый делитель введены логический элемент «И—

НЕ», два инвертора и вспомогательный дешифратор, на входы которого поданы прямые и инвертированные сигналы от генератора импульсов и блока управления, при этом выходы всех дешифраторов соединены со входами логического элемента «И вЂ” НЕ», выход которого соединен с одним из раздельных входов триггера.

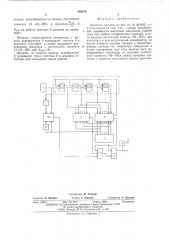

На чертеже представлена принципиальная структурная схема делителя частоты, который содержит генератор 1 импульсов, счетчик 2 с общей шиной обнуления, выполненный на триггерах, дешифратор 3 скважности, блок 4 управления, дешифратор 5, триггера 6, выходы 7 и 8, инвертор 9, вспомогательный дешифратор 10, инверторы 11, 12, логический элемент 13 «И — НЕ».

Делитель частоты работает следующим об5 разом.

Точное симметрирование выходного меандра (поддержание скважности равной двум) достигается за счет совпадения на логическом элементе 13 «И — НЕ» импульса с выхода де10 шифратора 3 и прямой или инверсной последовательности импульсов генератора 1 с выхода вспомогательного дешифратора 10 в зависимости от наличия в младшем разряде кода управляющего сигнала «О» или «1».

После прохождения на вход счетчика 2 «Г пр. импульсов в дешифраторе 3 происхо2

1 упр дит совпадение кода - р с дополнительным

20 2 кодом состояний триггеров счетчика 2.

На выходе дешифратора 3 появляется импульс положительной полярности, поступаю25 щий на логический элемент 13 «И — НЕ». При совпадении этого импульса с импульсами с выхода дешифратора 10 па выходе логического элемента 13 «И — НЕ» появляются импульсы отрицательной полярности, первый из ко30 торых опрокидывает триггер 6. Остальные им499674

Формула изобретения

Составитель М. Аудринг

Техред Т. Курилко

Корректор А. Дзесова

Редактор И. Шубина

Заказ 448/17 Изд. № 2127 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 пульсы, появляющиеся на выходе логического элемента 13 «И — НЕ» в пределах - "Р и

Nyp на работу триггера 6 влияния не оказывают, Импульс отрицательной полярности с выхода дешифратора 5 возвращает триггер 6 в исходное состояние, а также запрещает прохождение импульса с логического элемента

13 «И — НЕ» при Ny p — — 2".

Импульс со второго выхода дешифратора

5 производит сброс счетчика 2 в исходное состояние для очередного цикла работы.

Делитель частоты по авт. св.,% 401005, о тл и ч а ю щи и с я тем, что, с целью поддержа5 ния скважности выходных импульсов, равной двум при лю бом коэффициенте деления, в него введены логический элемент «И — НЕ», два ипвертора и вспомогательный дешифратор, на входы которого поданы прямые и инвертиро10 ванные сигналы от генератора импульсов и блока управления, при этом выходы всех дешифраторов соединены со входами логического элемента «И вЂ” HE», выход которого соединен с одним из раздельных входов триггера.