Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Своз Советских

Социалистических

Республик

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное K авт. свид-ву (22) Заявлено 21.11.72(21) 1847799/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано25.08.77.Бюллетень № 31 (45) Дата опубликования описания 26.00.77. (51) М. Кл, 11 С 15/ОО

Государственный комитет

Совете Министров СССР ео делам изооретений и открытий (53) ygy 681.327.6 (088.8) (72) Авторы изобретения

Г. B. Виталиев, А. Д. Гвинепадзе и P. В. Смирнов (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО! б

Бель изобретения - повышение аффективной емкости устройства. Для етого устройство содержит блокт сумматоров по модулю два по количеству блоков дешифраторов, первые входы которых подключены к выходам gp соответствующих дешифраторов опроса, выходы каждого предыдущего блока сумматоров подсоединены к вторым входам последующего блока сумматоров, а выходы последнего блока сумматоров связаны с соответст н

Изобретение относится к области запо,минающих устройств (ЗУ).

Известны ассоциативные запоминающие устройства (АЗУ), содержащие адресные запоминающие модули, разрядные шины которых подключены к входам соответствую щих детекторов, и блоки дешифраторов, onроса, входы которых подсоединены к выходам соответствующих блоков регистра опроса.

Однако в известных ассоциативных ЗУ с увеличением емкости адресных запоминающих модулей резко падает эффективность их использования. вующими адресными шинами адресных вано минающих модулей.

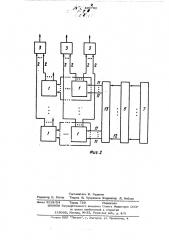

На фиг. 1 приведена блок схема устройст ва; на фиг. 2 — модифицированная блок-схе

g ма с использованием долговременных заломи нающих модулей.

Устройство состоит из адресных запоминающих модулей 1, разрядные шины 2 которых подключены к входам соответствую

g ..щих детекторов 3, и блоков 4 дешифраторов

5 опроса, входы которых подсоединены к выходам соответствующих блоков 6 регистр ра 7 опроса. Кроме того, устройство содержит блоки 8 сумматоров по модулю два по количеству блоков 4, Первые входы 9 блоков 8 подк аочены к выходам соответствую щих дешифраторов 5, выходы каждого предыдущего блока 8 подсоединены к вторым входам 10 последующего блока 8, а выходы последнего блока сумматоров связаны с соответствующими адресными шинами 1 1 модулей 1, Работа устройства осуществляется следующим образом, При записи произвольный код, посту "3 (42

3 пающий на регистр 7 опроса, преобразуеч ся дешифраторами 5 и блоками 8 сумматоров в код с равным числом единичных" и нулевых выходов блоков сумматоров (частный случай кода с равным весом).

Выходы последнего блока 8 возбуждают ровно половину адресных шин 11 модулей

1. В соответствующие моменты на разрядной шине 2, связанной с выбранным детектором 3, последовательно записывается, например, код "нуля", е в остальные моменты на этой шине предварительно записывает ся, например, код "единицы". Аналогично производится запись в ячейки, связанные с другими детекторами.

При считывании сод опроса с регистра

7 преобразуется соответствующими дешифраторами 5 и блоками 8 сумматоров В код * с равным весом. Возбуждаются одновременно все адресные шины 1 1, соединенные с суммато рами последней части, выходы которых соответствуют коду "единиць ", и.производится параллельный:опрос всех модулей 1. Соотношение сигнал помеха выбирается так, что И /2 сигналов "нуля воспринимаются детектором как "нулевой" сигнал, т. е. сиг нал совпадения (И - число адресных шин .модула), В той ячейке АЗУ, где произойдет полное совпадение, сигналы на выходе соот- ветствующего детектора будут "нулевые"

Во всех остальных ячейках на входах детек- торов будет один или несколько "единичных сигналов, что приводит к появлению на выходах этих детекторов "единичных сигналов, т. е. сигналов несовпадения. В остальном работа устройства аналогична работе извесь ных ассоциативных ЗУ..

Изобретение является схемной реализацией частного случая различимых кодов с равным весом. Эффективность использования оборудования АЗУ может быть lloeblllleHG эа счет применения в качестве преобразователей долговременных запоминающих модулей мод ле, ко торые позволяют реализовать любой, даже неразличимый, код с равным весом. С этой целью к выходам дешифраторов 5 опроса

1О могут быть присоединены адресные шины

12 долговременных запоминающих модулей

13, разрядные шины которых соединены с соответствующими адресными шинами 11 адресно к запоминающих модулей 1 (см. фиг и ). Работа устройства, изображенного на

21 фиг, 2, аналогична работе описанного уст ройства.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее адресные запоминающие модули, разрядные шины которых подключены к вхо дам соответствующих детекторов, и блоки дешифраторов опроса, входы которых подсое25 динены к выходам соответствующих блоков регистра опроса, о т л и ч а ю щ е е с я тем, что, с целью повышения эффективной емкости устройства, оно содержит, блоки сумматоров по модулю два по колиЧеству о блоков дешифраторов, первые входы которых подкхпочены к выходам соответствующих де шифраторов опроса, выходы каждого предыдущего блока сумматоров подсоединены к вторым входам последующего блока сумма

% торов, а выходы последнего блока суммато

pDB связаны с соответствующими адресными шинами адресных запоминающих модулей.

Составитель В. Рудаков

Редактор Н. Коган Техред В. Куприянов Корректор Л. Небола

Заказ 3118/84 Тираж 729 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР но делам изобоетений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

< тлиал ППП "Патент", r. Ужгород, ул, Проектная, 4