Устройство для контроля движения транспортного средства при переходе с одного пути на другой

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТИДЬСТВУ

Союз Советских

Социалистииеских республик (») 500129 (5Ц М. Кл. В 6ВС 43/00

Н 03 K 1/00 (6!) Дополнительное к авт. свид-ву (22) ЗаявленоОЗ.О2.72 (21) 1745577/27-11 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 25.01.76 Бюллетень № 3 (45) Дата опубликования описания 31.О3 76.- Гасударстаанный намнтет

Фаната Мнннстраа СССР на данам нзобратаннй н атхрытнй (53) уД 621.867(088.8) (72) Авторы .изобретения В. М. Голованевский, С. А. Каган, К. Н.. Новиков и Л. И. Тильман (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНОГО

СРЕДСТВА ПРИ ПЕРЕХОДЕ С ОДНОГО ПУТИ НА ДРУГОЙ

Изобретение касается устройства управ« ления конвейерными установками и может быть использовано в различных устройствазс

1 автоматики циклического действия, где требуется контроль поступления сдвинутых:., во времени сигналов.

Известные устройства контролируют пра вильность прихода сигналов только, одного датчика (датчика входа), но могут быть дополнены так, чтобы контролировать оба 10 датчика. Однако известные устройства при

: срабатывании формируют одйночньтй импульс, I а для приема -этого импульса и включения схемы сигнализации и зашиты требуются дополнительные устройства. 1б

Цель," .предлагаемого изобретенияповьтшенйе надежности контроля движения транспортного средства, Это достигается тем, что устройство снабжено блоком динамической памяти, 20 включаюшим в себя две ячейки запрета и ячейку задержки,-причем . к входу одной ячейки запрета по включены выходы ячееи.

*;а — — -1

I памяти, соединенных с датчиками пути, к входу другой ячейки - выходы датчиков пути, а каждый датчик соединен со считы« вающим входом одной ячейки памяти и подготавливающим входои другой.

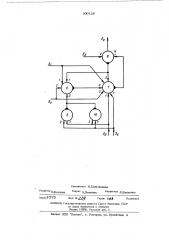

На чертеже показана функциональная схема устройства для контроля движения транспортного средства при переходе с одного пути на другой, построенная на ферриттранэисторных ячейках..На чертеже приняты следующие обозна чения: 1- вход подготовки; 2 - вход счи« тывания, 3 вход, гашения, 4 а ич - тер транзистора элементдь. Поэицийй .5 обозначены тактовые сигналы.(индекс указывает на условный порядок сигнала в тактовом цикле).

Елок динамической памяти построен на схеме запрета (ячейки 6 и 7) и элементе задержки (ячейка 8}. B ход схемы запрета подключен к . входу 2 подготовки ячейки 8, выход которой соединен с входа ми подготовки ячеек 6 и 7. К входу гашения ячейки 6 подключены выходы дололниъ тельных элементов памяти (ячейки 9 и

10), а входы подготсвки ячейки 7 соедин»50О129 ны датчиком пути, контролируемым сигналами 5 . 6 соответственно

Датчик пути (контролирующий сигнал

5 ) подключен к входу подготовки ячей5 ки 9 и к входу считывания ячейки 11, а датчик пути (контролирующий сигнал 5 ) — к подготавливающему и считывающему входам ячеек 9 и 10.

Устройство работает следующим образом. о

В исходном состоянии (при правильной очередности прихода сигналов) сигнал 5 подготавливают ячейку 6 блока динамической памяти и гасит ячейку 7. Ячейка

8 является неподготовленной. В зависимости от того, какбй из сигналов пришел последним, будет подготовлена одна из ячеек 9 или 10. Пусть последним пришел сигнал 5. Тогда к моменту прихода сигнала 6 ячейка 11 будет подготовлена. Сиг-. нал 5 может приходить первым и третьим тактовыми сигналами, например, во втором такте. Он подготовит ячейки 7, 9 и считывает ячейку 10. Последняя срабэтав, погасит ячейку 6. Таким образом, к моменту прихода сигнала ячейка 6 не будет подготовлена и схема запрета (ячейки 6 и 7) не сработает. Сигнал погасит ячейку 7 и вновь подготовит ячейку 6. В случае 30 прихода сигнала 5 схема будет работать аналогичным образом, только теперь гашение ячейки 6 осуществит ячейка 9.

Если сигнал приходит два раза подряд, то первый раз сигнал 5 подготовит ячей- 35 ки 6, 9, и считает ячейку 10, которая погасит ячейку 6. Второй раз сигнал 55 вновь подготовит ячейки 6 и 9, но считывание ячейки 10 не приведет к его сраба- 40 тыванию, так как он был не подготовлен (сигнал 5 не поступал).

Таким образом, окажутся подготовленными обе ячейки 6 и 7 схемы запрета, схема сработает под воздействием сигнала

5 и подготовит ячейку 8. Тактовый сигнал

6 вызовет срабатывание ячейки 8, а она вновь подготовит схему запрета, которая в свою очередь, подготовит в четвертом такте ячейку 8. О включении дина мической памяти будет свидетельствовать серия импульсных сигналов 5, снимаемых с ячейки 8. Аналогичным образом схема работает припоступлении два раза подряд сигнала 5

Подобным образом может быть построено устройство для проверки очередности поступления Л ) 2 сигналов. При этом для каждого проверяемого сигнала добавляется элемент памяти, который считывается проверяемым сигналом, подготавливается другим сигналом, сдвинутым относительно проверяемого во времени, а с выхода этого элемента подается сигнал гашения на ячей ку 7.

Предмет из обретения

Устройство для контроля движения транспортного средства при переходе с одного пути на другой, включающее датчики пути, ячейки памяти, количество которых соответствует количеству датчиков, о т л ич а ю щ е е с я тем, что, с целью повы— шения надежности контроля, оно снабжено блоком динамической памяти, включающим в себя две ячейки запрета и ячейку задерж ки, причем к входу одной ячейки запрета подключены выходы ячеек памяти, соединенных с датчиками пути, к входу другой ячейки - выходы датчиков пути, а каждый датчик соединен со считывающим входом одной ячейки памяти и подготавливающим входом другой.

500 129

Составитель Н.Глибовицкая

Те"ред H.xàíååâà

Корректор д,Брахнина

Изд. КООИ9

UHHHllH Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Редактор р Н.Козлова

Заказ« > Г 9

Тираж 9фД Подписное