Устройство для поиска псевдослучайного сигнала по задержке

Иллюстрации

Показать всеРеферат

Союз Советских

СРцивлмстических

Реснублмк (1ii 560528

3 (l с (61) Дополнительное к авт. свид-ву (Ц) Заявлено 08.07.74 (21) 2045ДХО/l8 24 с присоединением заявки №(23) Приоритет (43) Опубликовано 25.01.76 Бюллетень № Э (4Б) Дата опубликования описания 19.04.76

g ""--.- у. (51) М. Кл, Q 06F 15/34

Гооударстеенный комитет

Совете й!иниотроо СССР оо делом нзооретений н открытий (о!3) х Д1 681. 328:519.2 (088.8) (72) Ав горы изобретения Д. О. Яковлев, B. Н. Номоконов и М, В. Корепов (71) Заявитель Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) УСТРОЙСТВО ДЛЯ ПОИСКА ПСЕВДОСЛУЧАЙНОГО

СИГНАЛА ПО ЗАДЕРЖКЕ

Изобретение относится к цифровым уст ройствам для обработки сложных сигналов и может быть использовано в связных и радионавигационных системах различного назначения, модулируюший сигнал которых яв- 5 ляется двоичным псевдослучайным сигналом (ПСС), известным также под названием Ir последовательности или кода максимальной длины.

Основной задачей, которая возникает в 10 таких системах, является определение временной задержки принимаемого сигнала, что соответствует определению фазы сигнала при воздействии помех в канале связи и фазированию местного генератора ПСС, 15

Известно устройство для поиска псевдослучайного сигнала по задержке, содержащее коррелятор, соединенный одним пз входов с входом устройства, а выходом подключенный к пороговому элементу, Огра.-20 ничитель, соединенный с входом первого регистра, подключенного через переключатель к входу второго регистра, разрядные, выходы регистров через соответствуюшпе сумматоры по модулю два соединены с k- 2б входами мажоритарного элемента, подключенного через переключатель к другому входу коррелятора.

Однако в таком устройстве для поддержания высокой достоверности оценки фазы при больших вероятностях искажения сигнала но. обходимо увеличение кратности исправляемых ошибок, а в рамках известного устройства это возможно только за счет увеличения числа используемых проверок, т. е. за счет сушественного увеличения объема оборудования. Поэтому при естественных ограничениях объема оборудования достижи .мая достоверность оценки оказывается недостаточной для эффективной работы в условиях сильных помех. Это обусловлено жесткой детерминированностью работы известного устройства во время предварительной оценки фазы, при которой исправление ошибок осушествляется только в те-. чение и тактс в (режим б ) .

11ель изобретения — сокрацсенне времени поиска сигнала по задержке и ввода местНОГО генера ГОра B синх()он!!Ок! беэ увели

500528 чения длины регистров и числа сумматоров по модулю два.

Для этого предлагаемое устройство со« держит 1/2 (k+1)-входовой элемент И, 1/2 (k+1)-входовой элемент ИЛИ-НЕ и двухвходовой элемент ИЛИ-НЕ, причем входы 1/2 (k+1)-входовых элементов ИЛИ.

HE и И соединены с выходами суммато.ров по модулю два, подключенных с разрядным,выходам, второго регистра, а выходы 1/2 (k+1)-входовых элементов ИЛИНЕ и И через двухвходовой элемент ИЛИНЕ соединены с входом сброса коррелятора.

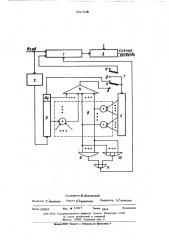

На чертеже изображена блок-схема пред16 лагаемого устройства.

Устройство содержит коррелятор 1, пороговый элемент 2, ограничитель 3, k-входовой мажоритарный элемент 4, два сдвиговых регистра - основной 5 и вспомогательс0 ный 6, общая длина которых равна (л, + 0 ), сдвоенный переключатель 7, сумматоры 8 по модулю два, 1/2 (k+1 ) -входовой элемент

И 9, 1/2 (k+1)-входовой элемент ИЛИ-HE

10 и двухвходовой элемент ИЛИ-HE 11.

Входная шина устройства соединена с одним из входов коррелятора 1, выход которого подключен к входу пороговой схемы

2. Выход схемы 2 является выходом всего устройства. Вход регистра 5 через ограничитель 3 подключен к входной шине устройства, выход регистра 5 через переключатель 7 соединен с входом рет истра 6. К выходам регистров 5 и 6 подключены входы сумматоров 8 по модулю два, выходы которых соединены с входами мажоритарного элемента 1, причем l/2(k+1) входов (т. е. большинство входов) мажоритарного элемента подключены к выходам тех сумматоров 8, которые связаны только с ячейка- 0 ми регистра 6, Параллельно 1/2(k+1) входам мажоритарного элемента 4 подключены входы элементов И 9 и ИЛИ-НЕ 10, выходы которых через элемент ИЛИ-НЕ 11 соединены с шиной сброса коррелятора 1.

Устройство работает следующим образом.

B исходном состоянии подвижные контакты переключателя 7 находятся в положении а и видеосигнал с выхода ограничителя 3 поступает в регистры 5 и 6 ° После. заполнения всех ячеек регистров 5 и б, т, е. (h. + t ) тактов, переключатель 7 устанавливается в положение О . При этом на вход регистра 5 продолжают поступать сигналы с выходе ограничителя 3, ана вход 55 регистра 6 и коррелятора 1 - сигналы с выхода мажоритарного элеменга 4. Сумматоры 8 подключены к выходам ячеек регистров 5 и 6 так, что на выходе каждого сумматора вин аба1ьи ается сигнал, соответ- ф ствующий значению раз яда а и по боль0 шинству одинаковых сигналов мажоритарного элемента вырабатывает исправленное значение а . Так как большая честь сум0 маторов 8 соединена с рег истром 6, после исправления всех ошибок в регистре 6 сигналы на выходе мажоритарного элемента 4 становятся независимыми от принимаемых сигналов. В результате этого регистр 6 вместе с цепью обратной связи, замыкающейся через соответствующие сумматоры и мажоритарный элемент, автоматически переходит в режим работы местного генера тора ПСС.

Полное совпадение сигналов на выходах сумматоров, связанных с регистром 6, устанавливается с помощью ементов 9, 10, и 11, составляющих схему контроля состояния регистра 6. На выходе элемента ИЛИНЕ 11 появляется сигнал "1", если не все сигналы на входах элементов 10 и 9 одинаковы; в противном случае на выходе элемента ll устанавливается постоянный нулевой сигнал, свидетельствующий об окончании процесса исправления ошибок, При этом прекращается подача сигнала на сброс накопителя в корреляторе 1 и начинается корреляционный анализ правильности вхождения в фазу, (Предполагается, что взаимный сдвиг сигналов, поступающих на входы коррелятора 1, компенсирован) . Если результат анализа отрицателен, то предпринимается новая попытка поиска.

Таким образом, ввод принимаемых сигналов в регистры предлагаемого устройства производится так же, как в прототипе, но исправление ошибок, в отличие от прототипа, осуществляется вплоть до полного совпадения содержимого основного регистра 6 с участком используех1ого псевдослучайного сигнала, Г1ри этом время исправления не ограничивается тактами, как в прототипе, а определяется реальным числом произошедших ошибок. Если ошибок не было, то корреляционная проверка вхождения в фазу начинается сразу же после заполнения регистров 5 и 6. Аналогичным образом предлагаемое устройство реагирует на появление ошибок, гарантировано исправляемых мажоритарным элементом. При большей кратности ошибок процесс исправления продолжается и в нем используются дополнительные импульсы принимаемого сигнала. Тем самым устройство приобретает новое свойство самоадаптации к условиям помеховой обстановки в канале связи, а некоторое увеличение времени исправления ошибок I с избытком компенсииспр

500528 г руется сокращением среднего числа попыток поиска (с учетом того, что Т >) а Т ). испр

Предмет изобретения

Устройство для поиска псевдослучайного сигнала по задержке, содержащее коррелятор, соединенный одним из входов с входом устройства, а выходом подключенный к пороговому элементу, ограничитель, соединенный с входом первого регистра, подключенного через переключатель к входу второго регистра, разрядные выходы регистров через соответствующие сумматоры по модулю два соединены с к входамп маж тарного элемента, подключенного через переключатель к другому входу коррелятора, о т и ч а ю ш о е с а т " что, с пелью повьп:ения средне о бь ттздействпя, устройство содержит 1/2(k+1 )-входовой элемент И, 1/2(kt 1 ) -входовой элемент

: ИЛИ-HE и двухвхоаовой элемент ИЛИ-НЕ, причем входы 1/2(1+1)-входовых элементов ИЛИ-HE и И соединены с выходами сумма)о.-. по модулю два, подключенных к разрядным выходам второго регистра, а выходы 1/2(k+1)-входовых элементов ИЛИHF и И через двухвходовой элемент ИЛИ, НЕ соединены со входом сброса коррелятора.

50(2 528

Заказ 6304 . Изд. М 1357 Тираж 864

Ц1П. ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская иаб., 4

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 Составитель В. Жовинскйй

Редактор Т.11вановв Техред 3.Тараненио Корректор А.Галахова