Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

Ватвйтио i »!.е» нс.(2Каю бнблко тем» ЛБА

О П И C А Н И Е (1!) 5QI42I

ИЗОБРЕТЕН ИЯ

Соют Co!;«;;t:Kèõ

Соииалис!и !вских

РЕСнтблнK (61) Дополнительное к авт. свид-в (22) Заявлено 18.11.74 (21) 2076672 18-24 (51) М. Кл.- 6 11С 15, 00 с ирисоедииеиием заявки ЛЪ

)ос)!дарственный комитет

Совета Министров СССР но делам изобретений и открытий (23) Приоритет

Опубликов",»o 30.01.76. Бюллетень Л% 4

Дата опубликования описания 30.07.76 (53) УДК 681.327 (088.8) (72) Авторы изобретения

Е. П. Бал".шов, В. В. Васильев и T. Э. Темирханов (71) Заявитель

Ленинградский ордена Ленина электротехнический институт им. В. И. Ульянова (Ленина) (54) ЛОГИЧЕСКОЕ ЗАПОМИ11А1ОЩЕЕ УСТРОЙСТВО

Изобретение относится к заломинающим устройствам.

Известно логическое запоминающее устройство, содержащее блоки памяти, адресные входы которых подключены к регистру адреса, информационные входы через последовательно соединенные элементы «ИЛИ» и

«И» первой группы — к выходам регистра слова и элементов «НЕ», а управляющие входы через последовательно соединенные элементы «И» и «ИЛИ» второй группы к выходам первых и вторых элементов «И» третьей грулпы.

Ограниченность области применения такого устройства вызвана невозможностью реализации в устройстве полного набора логических операций.

Предлагаемое устройство отличается от известного тем, что в него введены дополнительный регистр слова и дополнительные элементы «НЕ», входы которых подключены к выходам дополнительного регистра слова и информационным входам первых элементов

«И» третьей группы, а выходы — к информационным входам вторых элементо в «И» третьей группы.

Это позволяет расширить область применения устройства.

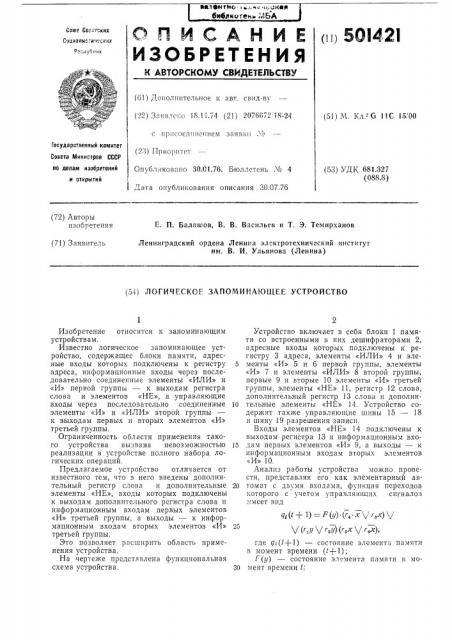

На чертеже представлена функциональная схема устройства.

Устройство включает в себя блоки 1 памяти со встроенными в них дешифраторами 2, адресные входы которых подключены к регистру 3 адреса, элементы «ИЛИ» 4 и эле5 менты «И» 5 и 6 первой группы, элементы

«И» 7 и элементы «ИЛИ» 8 второй группы, первые 9 и вторые 10 элементы «И» третьей группы, элементы «НЕ» 11, регистр 12 слова, дополнительный регистр 13 слова и дополни1О тельные элементы «НЕ» 14. Устройство содержит также управляющие шины 15 — 18 и шину 19 разрешения записи.

Входы элементов «НЕ» 14 подключены к выходам регистра 13 и информационным вхо15 дам первых элементов «И» 9, а выходы — к информационным входам вторых элементов

«И» 10.

Анализ работы устройства можно провести, представляя его как элементарный ав20 томат с двумя входами, функция переходов которого с учетом управляющих сигналов ..меет вид

q>(t+ 1) = Р(у) (r4.õ r,õ), / (у1у /! 2у) (! 3Х \/ 4Х)з где !1!(т+1) — состояние элемента памяти в момент времени (!+1);

1 (у) — состояние элемента памяти в мо30 мент времени 1, 501421

q=O хЛу уЛх уЬх хну х.i. y у-х уЯх у/х уАх уЯх у-х уVx хЛу у- х у у у х х >у х\/у у-х

Формула изобретения — r,« — управляющие сигналы; х и у — двоичные переменные.

Реализуемые таким элементарным автоматом логические операции над переменными х и у при различных его исходных соРаботу устройства поясним на примере реализации логической операции «сумма по модулю 2» между двумя двоичными переменными х и у. Для этого на регистр 12 слова считывается из блоков 1 переменная х, а на дополнительный регистр 13 — переменная у и устанавливается на управляющих шинах 16, 17 единичное значение сигналов, а на шинах 15, 18 — нулевое. При такой комбинации сигналов на управляющих шиЛогическое запоминающее устройство, содержащее блоки памяти, адресные входы которых подключены к регистру адреса, информационные входы через последовательна соединенные элементы «ИЛИ» и «И» первой группы — к выходам регистра слова и элементов «НЕ», а управляющие входы через последовательно соединенные элементы «И» и «ИЛИ» второй группы — к выходам первых и вторых элементов «И» третьей групстояниях и комбинациях управляющих сигналов, полученные из данного выражения, приведены в таблице, где S — сигнал на информационном входе блока памяти, R — сиг5 нал на шине 19.

Выполняемая логическая операция при нах и наличии сигнала на шине 19 содержимое обоих регистров 12, 13 через элементы «НЕ» 11 и 14, «И» 6, 9, «ИЛИ» 4, 8 и «И»

7 передаются в ячейку памяти блоков 1, где хранится переменная у, адрес которой устанавливается при помощи регистра 3 адреса в дешифраторе 2. Результат операции получается в выбранной ячейке блоков 1 после окончания режима записи.

15 пы, отличающееся тем, что, с целью повышения информационной емкости устройстEBB, оно содержит дополнительный регистр слова и дополнительные элементы «НЕ», входы которых подключены к выходам дополнительного регистра слова и информационным входам первых элементов «И» третьей группы, а выходы — к информационным входам вторых элементов «И» третьей

25 группы.

501421

1Е

Составитель В. Рудаков

Техред М. Семенов

Редактор И. Грузова

Корректор О. Тюрина

Типография, пр, Сапунова, 2

Заказ 1682/4 Изд. № 1437 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5