Устройство для генерации одиночных импульсов

Иллюстрации

Показать всеРеферат

(i i1 5GI 47G

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Ресауолии (61) Дополнительное к авт. свид-ву (22) Заявлено 17,04.74 (21) 2017315/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.01.76. Бюллетень № 1

Дата опубликования описания 01.04.76 (51) М. Кл е Н ОЗК 3/78

Государствеииый комитет

Совета Министров СССР оо делам изобретеиий и открытий (53) УДК 621.373.4 (088.8) (72) Авторы изобретения

В. A. Медведев и А. И, Ткаченко (71) Заявитель

Научно-исследовательский институт управляющих вычислительных машин (54) УСТРОЙСТВО ДЛЯ ГЕНЕРАЦИИ

ОДИНОЧ НЫХ ИМПУЛЬСОВ

Изобретение относится к радиотехнике и может быть использовано в устройсгвах преобразования, об|работки и передачи информации.

Известно у стройство для генерациями одиночных,импульсов, содержащее RS-триггер, S вход которого подключен к первому входу выходного логического элемента «И вЂ” НЕ», выход которого соединен с R входом RS-приггера н с первым входом первого логического элемента «И вЂ” НЕ», второй вход которого подключен к выходу RS-григгера, а выход первого логического элемента «И вЂ” НЕ» соединен с вторым входом выходного логического элемента «И вЂ” НЕ», третий вход которого подключен к шине тактовых сигналов.

Цель изобретения — повышение стабильности длительности выходных импульсов.

Это достигается тем, что в предлагаемое устройство введен логический элемент «НЕ» и D-триггер, выход которого соединен с S входом RS-триггера, первый вход D-триггера подключен к шине асинхронных сигналов, а второй вход D-триггера через логический элемент

«НЕ» соединен с третьим входом выходного логического элемента «И вЂ” HE».

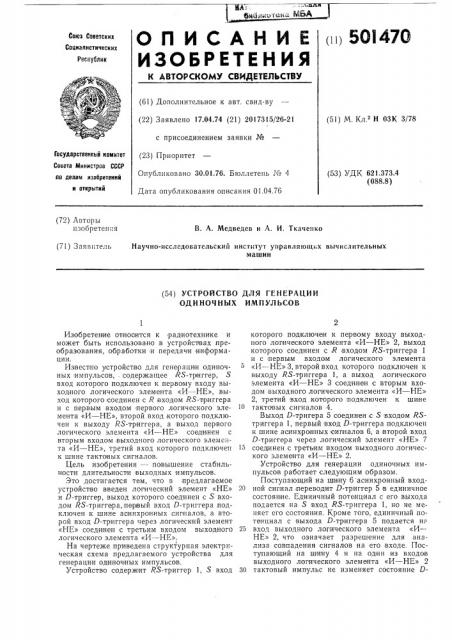

На чертеже приведена структурная электрическая схема предлагаемого устройства для генерации одиночных импульсов.

Устройство содержит RS-триггер 1, S вход которого подключен к первому входу выходного логического элемента «И вЂ” НЕ» 2,,выход которого соединен с 1т входом RS-триггера 1 и с первым входом логического элемента

«И — НЕ»3, второй вход которого подключен к выходу RS-триггера 1, а выход логического элемента «И вЂ” НЕ» 3 соединен с вторым входом выходного логического элемента «И вЂ” НЕ»

2, третий вход которого подключен к шине

10 тактовых сигналов 4.

Выход D-тригера 5 соединен с $ входом RSтриггера 1, первый вход D-триггера подключен к шине асинхронных сигналов 6, а второй вход

D-триггера через логический элемент «НЕ» 7

15 соединен с третьим, входом выходного логического элемента «И вЂ” HE» 2.

Устройство для генерации одиночных импульсов:работает следующим образом.

Поступающий на шину 6 асинхронный вход20 ной сигнал переводит D-триггер 5 в единичное состоян ие. Единичный потенциал с его выхода подается на S вход RS-триггера 1, но не меняет его состояния. Кроме того, единичный потенциал с выхода D-триггера 5 подается на

25 вход выходного логического элемента «И—

НЕ» 2, что означает разрешение для анализа совпадения сигналов на его входе. Поступающий на шину 4 и на один из входов выходного логического элемента «И вЂ” НЕ» 2

30 тактовый импульс не изменяет состояние D501470

Формула изобретения

Составитель Ю. Еркин

Техред М. Семенов

Корректор А. Дзесова

Редактор E. Караулова

Заказ 519/12 Изд. № 1037 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобпетений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 триггера 5, но обеспечивает совпадение единичных уровней потенциалов на всех трех входах выходного логического элемента

«И — HE» 2 и наличие нулевого потенциала,на его выходе. Нулевой потенциал передается на один из входов логического элемента «И вЂ” НЕ»

3, состояние кото рого не изменяется. RS-триггер 1 переключается, и на его выходе устанавливается единичный потенциал.

После окончания тактового импульса нарушается условие совладения сигналов на входах выходного логического элемента «И вЂ” НЕ»

2, и на его выходе и на выходе 8 устройства устанавливается единичный потенциал. С выхода выходного логического элемента «И вЂ” 15

НЕ» 2 единичный потенциал передается на вход логического элемента «И вЂ” НЕ» 3 и на

R вход RS-триггера 1, но при этом состояние триггера не изменяется, а состояниелогического элемента «И вЂ” HE» Зизменяется вследствие 20 совпадения единичных сигналов на его входах. На выходе логического элемента «И вЂ” НЕ»

3 устанавливается нулевой потенциал, который выполняет функцию запрета совпадения сигналов на входах выходного логического 25 элемента «И вЂ” НЕ» 2 и поддерживает единичный потенциал на выходе 8 устройства.

Каждый последующий тактовый импульс не может изменить состоя ния устройства. После окончания асинхронного входного сигнала D- 30 триггер 5 в промежутке между тактовыми импульсами изменяет свое состояние, и на его выходе устанавливается нулевой потенциал, который передается на соответствующий вход выходного логического элемента «И вЂ” HE» 2 и на S вход RS-триггера 1. С этого момента

D-триггер берет на себя функцию запрета на выходе выходного логического элемента «И—

НЕ» 2. Под влиянием нулевого потенциала с выхода D-триггера 5 на выходе логического элемента «И вЂ” НЕ» 3 устанавливает единичный потенциал. Наличие нулевого потенциала на выходе 8 устройства соответствует существованию одиночного импульса.

Устройство для генерации одиночных импульсов, содержащее RS-триггер, S вход которого подключен к первому входу выходного логического элемента «И вЂ” НЕ», выход которого соединен с R входом RS-триггера и с первым входом первого логического элемента

«И — НЕ», второй вход которого подключен к выходу RS-триггера, а выход первого логического элемента «И вЂ” НЕ» соединен с вторым входом .выходного логического элемента

«И — HE», третий вход которого подключен к шине тактовых сигналов, о т л и ч а ю щ е е с я тем, что,,с целью повышения стабильности дл ительности выходных им пульсов, в него введен логический элемент «НЕ» и D-триггер, выход которого соединен с S входом RS-триггера, первый вход D-триггера подключен к шине асинхронных сигналов, а второй вход

D-триггера через логический элемент «НЕ» соединен с третьим входом выходного логического элемента «И вЂ” HE».