Анализатор пакетов ошибок

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 50l490

ИЗОБРЕТЕНИЯ

Gaea Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 10.02.72 (21) 1747228/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.01.76. Бюллетень № 4

Дата опубликования описания 26.04.76 (51) М. Кл. Н 04L 1/00

Государственный комитет

Совета Министров СССР (53) УДК 621.317.799 (088.8) по делам изобретений н открытий (72) Авторы изобретения

А. И.Иванюк и В. С. Поздняков

Новосибирский электротехнический институт (71) Заявитель (54) АНАЛИЗАТОР ПАКЕТОВ ОШИБОК

Изобретение относится к области вычислительной техники, телемеханики, связи и может быть использовано при исследовании статистических характеристик каналов передачи данных.

Известен анализатор пакетов ошибок, содержащий триггер, вентиль, счетчик и дешифратор длин пакетов, причем выход вентиля соединен с входом счетчика, выходы счетчика — с входами дешифратора длин пакетов, считывающий вход дешифратора длин пакетов — с входом триггера, а выход триггера подключен к управляющему входу вентиля.

Выделение пакетов ошибок в известном анализаторе осуществляется по критерию интервала объединения Мд .

Цель изобретения — упрощение анализатора пакетов ошибок.

Это достигается путем введения в анализатор запоминающих схем и дешифратора «1» в запоминающей схеме старшего разряда.

Входы запоминающих схем подключены к выходам дешифратора длин пакетов, а их выходы — к входам дешифратора «1» в запоминающей схеме старшего разряда. Вход устройства соединен с входом триггера, а выход счетчика подключен к шине «Сброс», которая соединена с вторым входом триггера, с входами «Сброс» счетчика, запоминающих схем и входом «Считывание» дешифратора «1» в запоминающей схеме старшего разряда.

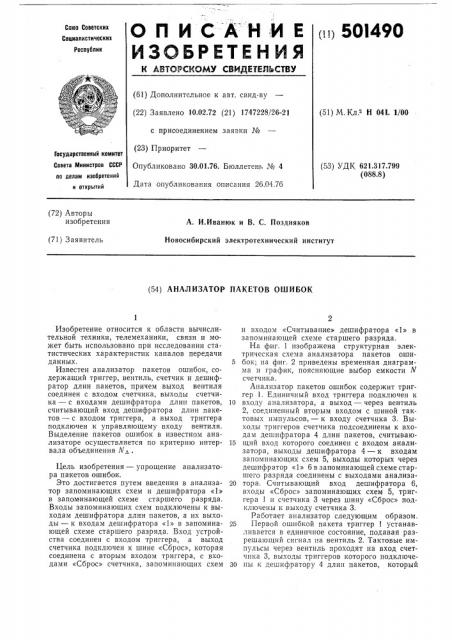

На фиг. 1 изображена структурная электрическая схема анализатора пакетов оши5 бок; па фиг. 2 приведены временная диаграмма и график, поясняющие выбор емкости A" счетчика.

Анализатор пакетов ошибок содержит триггер 1. Единичный вход триггера подключен к

10 входу анализатора, а выход — через вентиль

2, соединенный вторым входом с шиной тактовых импульсов, — к входу счетчика 3. Выходы триггеров счетчика подсоединены к входам дешпфратора 4 длин пакетов, считываю15 щий вход которого соединен с входом анализатора, выходы дешифратора 4 — к входам запоминающих схем 5, выходы которых через дешифратор «1» 6 в запоминающей схеме старшего разряда соединены с выходами анализа20 тора. Считывающий вход дешифратора 6, входы «Сброс» запоминающих схем 5, триггера 1 и счетчика 3 через шину «Сброс» подключены к выходу счетчика 3.

Работает анализатор следующим образом.

25 Первой ошибкой пакета триггер 1 устанавливается в единичное состояние, подавая разрешающий сигнал на вентиль 2. Тактовые импульсы через вентиль проходят на вход счетчика 3, выходы триггеров которого подключе30 ны к дешифратору 4 длин пакетов, который обеспечивает разнесение пакетов по и разрядам в соответствии с их длительностью. Считывание состояния счетчика 3 и дешифратора

4 осуществляется с появлением каждой ошибки пакета, и результаты считывания запоминаются в схемах 5 до тех пор, пока на вход счетчика 3 не поступят N тактовых импульсов, В этот момент считывается состояние запоминающих схем с помощью дешифратора б, выявляющего «1» в запоминающей схеме старшего разряда, т. е. результат опроса состояния счетчика 3 последней ошибкой пакета. Результат считывания состояния запоминающих схем заносится в соответствующий счетчик регистрирующего устройства 7, после чего тем же сигналом с выхода счетчика 3 сбрасываются запоминающие схемы, входной триггер и сам счетчик. Анализатор пакетов ошибок готов к приему следующего пакета.

В анализируемой последовательности ошибок с помощью анализатора выделяются временные отрезки длиной N тактов, начинающиеся ошибкой (фиг, 2, а). При правильно выбранной величине N каждый такой отрезок перекрывает один пакет ошибок или одиночную ошибку. Алгоритм выбора N поясняется графиком на фиг. 2, б, отражающим зависимость числа отрезков, т. е. числа пакетов N<, образовавшихся при анализе потока ошибок, от величины N. Кривая N< — — f(N) строится по данным параллельной обработки анализируемого потока ошибок или по данным многократных исследований потока ошибок, запи501490

4 санного на какой-либо носитель, Оптимальным значением N«, является значение близкое к точке сопряжения участков с большим и малым наклонами. Очевидно, что эта величина близка к максимальной длине пакета. Выбор N,, всегда возможен, так как пакеты ошибок имеют конечную длину и большую часть времени передача информации идет без искажений.

Формула изобретения

Анализатор пакетов ошибок, содержащий триггер, вентиль, счетчик и дешифратор длин пакетов, причем выход вентиля соединен с входом счетчика, выходы счетчика подключены к входам дешифратора длин пакетов, считывающий вход дешифратора длин пакетов соединен с входом триггера, а выход триггера подключен к управляющему входу вентиля, отличающийся тем, что, с целью упрощения, в него введены запоминающие схемы и дешифратор «1» в запоминающей схеме старшего разряда, причем входы запоминающих схем подключены к выходам дешифратора длин пакетов, а их выходы — к входам дешифратора «1» в запоминающей схеме старшего разряда, вход устройства соединен с входом триггера, а выход счетчика подключен к шине «Сброс», которая соединена с вторым входом триггера, с входами «Сброс» счетчика, запоминающих схем и входом «Считывание» дешифратора «1» в запоминающей схеме старшего разряда.

501490

vu2. 1

Корректор Л Орлова

Редактор И. Грузова

Заказ 715/7 Изд. № 1103 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Пюмок

ОшаРок

+onm

Р) 9Ъ г.2

Составитель A. Рассмотров

Техред Е. Подурушина