Демодулятор дискретных сигналов с фазоразностной модуляцией

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

ОПИСАНИ

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬ

Республик (61) Дополнительное к авт. свид-ву—

27/18

27/22 (22) Заявлено 1!.03.74 (21) 2004303/26 с присоединением заявки— (23) Приоритет— (43) Опубликовано 05.02.76. Бюллетен (45) Дата опубликования описания 17.0

Государственный комитет

Совета Министров СССР ло делам изобретений н открытнн (72) Авторы изобретения

В. С. Гиршов, О, В. Кустов и С. И. Лутовинов (71) Заявитель

Ленинградский электротехнический институт связи им. проф. М. А. Бонч-Бруевича (54) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ

С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ

Изобретение относится к технике связи, может использоваться в системах передачи информации.

Известен демодулятор дискретных сигналов с фазоразностной модуляцией, содержащий входные ключевые перемножптели, соединенные с соответствующими интеграторами-сумматорами и подключенные управляющими входами к выходам KDMIIBpBTopoB, на сигнальные входы которых подаются сигналы, задержанные на одну посылку, а управляющие входы подключены к выходу генератора линейно изменяющегося напряжения, и сумматоры аналоговых величин, входы которых подключены к выходам соответствующих интеграторов-сумматоров, а выходы — к решающей схеме.

Цель изобретения — расширение динами ecI oro диапазона демодулятора.

В предлагаемый демодулятор введены схемы вычисления модулей входных сигналов, соединенные с дополнительным сумматором, выход которого подключен к генератору линейно изменяющегося напряжения.

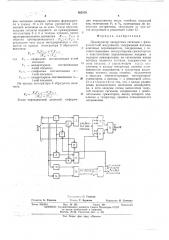

На чертеже приведена блок-схема демодулятора.

Входные ключевые перемножителн 1 — 4 соединены с соо.лветслвующими интеграторами-сумматорами 5 и б и подключены управляющими входами к выходам компараторов

7 и 8. На сигнальные входы компараторо подаются сигналы, задержанные на одну посылку, а управляющие входы подключены к выходу генератора линейно изменяющегося напряжения 9.,Входы сумматоров .аналоговых величин 10 и 11 подключены к выходам соответствующих интеграторов-сумматоров 5 н б, а выходы — к решающей схеме 12. Схемь. вычисления модулей входных сигналов 18 и

14 C 0e II H H 0 H bl C 3 O II 0 JI H H T e Jl b H bI M сумматором

15, выход которого подключен к генератору линейно изменяющегося напряжения 9.

Устройство работает следующим образом.

Сигналы из канальных фильтров прием15 ника, содержащие синфазные и квадратурные составляющие и-ной посылки, передаются на ключевые перемножители 1 — 4, а сип фазные и квадратурные саста вляющне n—

1-вой насылая- на ком параторы 7 и 8, которые сравнивают входные сигналы с линейно изменяющимся напряжением генератора 9 и формируют временные интервалы, в течение которых входные сигналы подаются на интеграторы-сумматоры 5 и б.

Генератор 9 формирует линейно изменяющееся напряжение, скорость изменения которого прямо пропорциональна сумме модульных величин синфазной и квадратурной составляющих принимаемого сигнала, которая зо получается на выходе сумматора 15. МодульБО2518

Формула изобретения

15 соста,вляющая

Х„у,. 1 — Y,Y„ — IX.I+ l У вЂ”.

Знаки передаваемой двоичной

25 информа.1 (.

" >2 дыха

Г.„ рс тзр "л

Со"-.авитель О. Тихонов

Текред Т, Курилко

Редактор Б. Федотов

Корректор И. Симкина

Заказ 562/854 Изд. № 256 Тираж 864 Подписное

LIHHHHI I Государственного комитета Совета Министров СССР по делам изобретений и открытий

Моеква, 7К-35, Раушскан. наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» ные величины входных сигналов формируются в схемах 13 и 14 путем умножения аналоговой величины на ее знак. Таким образом. входные сигналы подаются на суммирующие интеграторы 5 и 6 в течение времени, прямо пропорционального значениям Х„;, У;, и обратно пропорционального )Х + )у (, в результате чего после интегрирования и сложения на выходе интегратора 5 образуется величина:

Х„У „, + Y„Y„ где Մ— сиыфаз ная составляющая и-ной посылки;

Y, — квадратур хая л.вой посылки;

Х„, — синфазная составляющая ив

1-zoA аосылхи;

Y — квад ратурная составляющая и—

1- вой посылки. .На выходе интегратора б образуется величина: ции определяются после линейных операций над величинами V) и Vg, проводимых по известным алгоритмам, зависящим от кра I:-)ости модуляции в решающей схеме 12.

Демодулятор дискретных сигналов с фазоразностной модуляцией, содержащий входные ключевые перемножители, соединенные с соответствующими интеграторами-сумматорами и подключенные управляющими входами к выходам компараторов, на сигнальные входы которых подаются сигналы, задержанные на одну посылку, а управляющие входы подключены к выходу генератора линейно изменяющегося напряжения, и сумматоры аналоговых величин, входы которых подключечы к выходам соответствующих интеграторовсумматоров, а выходы — к решающей схеме, отл ич,аю щий ся тем, что, с целью расширения динамического диапазона демодулятора, в него введены схемы вычисления модулей входных сигналов, соединенные с дополнительным сумматором, выход которого подключен к генератору линейно изменяющегося напряжения.