Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

САН ИЕ

ОП И

ИЗОБРЕТЕНИЯ п 503240

Союв Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 29.05.74 (21) 2030500, 18-24 (51) М. Кл G 06F 9/16 с присоединением заявки ЛЪ

Государственный комитет

Совета Министров СССР ло делан и1обретаннй и открытий (23) Приоритет

Опубликовано 15.02.76. Бюллетень Ме 6

Дата опубликования описания 19.04.76 (53) УДК 681,325(088.8) (72) Авторы изобретения

К). М, Евдолюк, C С. Жернова, Л. Н. Колонина, Ж. Р. Маслова, В. Н. Степанов и Е. К. Ульянова (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изоб ретение относится к вычислительной технике, в частности к,реализации микроподпрограмм в микропрограммном процессоре.

Известны микропрограммные устройства управления, содержащие блок памяти микрокоманд, регистр адреса, регистр микрокоманд, регистр кода операции, блок управления, дешифраторы кода микрокоманды и кода ветвления соответственно, первый и второй элементы «ИЛИ», первый, второй и третий элементы «И», причем выход блока памяти микрокоманд соединен с входом регистра,миирокоманд, первый выход которого соединен через дешифратор кода микрокоманды с первых входом блока управления, второй выход регистра микрокоманд соединен с входом дешифратора кода ветвления, первый выход. которого соединен с вторым входом блока управления, первый выход последнего соединен с первым входом первого элемента

«ИЛИ», а его второй вход — с третьим выходом регистра микрокоманд, четвертый выход которого соединен с первым входом первого элемента «И», второй вход элемента «И» соединен с вторым выходом блока управления и с первыми входами второго и третьего элементов «И», второй вход второго элемента «И» соединен с выходом регистра кода операции, а выход соединен с первым входом второго элемента «ИЛИ», второй вход которого соединен с выходом первого элемента «И», а выход — с первым входом регистра адреса, второй вход которого соединен с выходом третьего элемента «И», а выход — с входом блока памяти микрокоманд, второй вход третьего элемента «И» соединен с выходом первого элемента «ИЛИ».

Однако в известных устройствах для реализации возврата из микроподпрограммы имеет10 ся специальный регистр возврата, что увеличивает затраты оборудования.

С целью упрощения устройства оно дополнительно содержит элемент «НЕ» и третий элемент «ИЛИ», первый вход которого шиной

15 начала операции соединен с третьим выходом блока управления, второй вход шиной возврата соединен со вторым выходом дешифратора кода ветвления, а выход соединен непосредственно с третьим входом второго элемента

20 «И», а через элемент «HE» — с третьим входом первого элемента «И».

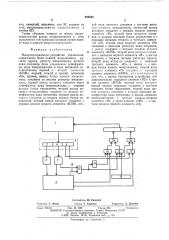

На чертеже показана .блок-схема предлагаемого микропрограммного устройства управления.

25 Работа процессора осуществляется путем выборки из блока 1 памяти микрокоманд в регистр 2 микрокоманд и исполнения последовательности микрокоманд. Регистр 2 микрокоманд содержит поле 3 для указания кода ми30 крокоманды, поле 4 для указания кода ветвле503240 ния при необходимости условных ветвлений по результату выполнения данной или предыдущей микрокоманды, поле 5 для указания адреса следующей микрокоманды, Код микрокоманды из поля 3 и код ветвления из поля

4 дешифруются дешифратором 6 кода микрокоманды и дешифратором 7 кода ветвления соответственно и воздействуют на блок управления 8.

Адрес выбираемой микрокоманды образуется в регистре 9 адреса. При выполнении текущей команды ее код хранится в регистре 10 кода операции.

По окончании выборки очередной команды процессора из оперативной памяти ее код операции передается в регистр 10 кода операции и хранится там до конца выполнения команды. Вход в микропрограмму выполнения команды осуществляется путем выборки микрокоманды, имеющей в адресном поле 5 нулевой код, а в поле 3 код, по которому устройство управления 8 возбуждает шину 11 начала операции, при этом на выходе элемента «ИЛИ»

12 появляется сигнал, разрешающий передачу содержимого регистра 10 .кода операции через второй элемент «И» 13 и второй элемент

«ИЛИ» 14 в старшие разряды .регистра 9 адреса.

Элемент «НЕ» 15 в этом случае блокирует входы первого элемента «И» 16, передающего старшие разряды адресного поля 5 в старшие разряды регистра 9 адреса.

В младшие разряды регистра 9 адреса через первый элемент «ИЛИ» 17 и третий элемент «И» 18 передается нулевой код из младших разрядов адресного поля 5.

Таким образом, процессор .переходит к микропрограмме выполнения команды.

При выполнении последовательности микрокоманд в микропрограмме входы и выход третьего элемента «ИЛИ» 12 имеют нулевое значение, а выход элемента «НЕ» — единичное значение, и адрес следующей микрокоманды образуется передачей в регистр адреса 9 старших разрядов адресного поля 5 через первый элемент «И» 16 и второй элемент

«ИЛИ» 14, а младших разрядов адресного поля 5 через первый элемент «ИЛИ» 17 и третий элемент «И» 18, Прием информации в регистр 9 адреса стробируется сигналом, вырабатываемым блоком управления на втором выходе.

В случае выполнения микрокоманды с ветвлением в поле 4 ветвления записывается соответствующий код ветвления, который после дешифрации в дешифраторе 7 кода ветвления вырабатывает,на выходе блока управления код младших разрядов адреса в соответствии с результатами выполнения текущей и предыдущей микрокоманды, который через первый элемент «ИЛИ» 17 и третий элемент «И» 18 передается в младшие разряды регистра адреса.

Младшие ветвящиеся разряды адреса в адресном поле 5 должны иметь при этом нулевое

ЗО

65 значение. Старшие разряды регистра 9 адреса в данном случае определяются старшими разрядами адресного поля 5.

При необходимости входа в общие микроподпрограммы в адресное поле 5 записывается адрес .начала микроподпрограммы. В последней микрокоманде микроподпрограммы в поле ветвления записывается код ветвления, возбуждающий шину 19 возврата дешифратора 7 кода ветвления, а в адресном поле 5— адрес, отличный от нуля.

В конце выполнения микроподпрограммы происходит автоматический возврат в фиксированную ячейку зоны выполнения текущей команды. Затем в ходе выполнения команды может быть осуществлен переход к другой микропрограмме, после выполнения которой происходит автоматический возврат в другую. фиксированную ячейку зоны выполнения команды, определяемую содержанием младших разрядов адресного поля 5.

Рассмотрим,,например, выполнение команды умножения с плавающей запятой и нормализацией результата. Для выполнения указанной команды используются следующие микроподпрограммы: микроподпрограмма сложения порядков; микроподпрограмма умножения мантисс; микроподпрограмма нормализации результата.

Запишем микрокоманду в виде а а аз, где а, — код микрокоманд, а — поле ветвления;

a> — поле адреса следующей микрокоманды.

Пр имем, что возбуждение шины Возвр ата происходит при фиксированном значении поля ветвления а =1 и указанная команда умножения имеет код операции 57.

Тогда в последней микрокоманде завершения цикла выборки команды из оперативной памяти и ооразования исполнительного адреса поле адреса а =0, и процессор входит в микропрограмму выполнения команды умножения,.начиная с адреса 570, По окончании выборки операнда из оперативной памяти осуществляется переход в микроподпрограмму сложения порядков, последняя микрокоманда которой имеет вид а1 11.

По окончании выполнения этой микрокоманды осуществляется переход в ячейку 571. Затем процессор выполняет некоторые подготовительные операции и переходит к микроподпрограмме умножения мантисс, последняя микрокоманда которой имеет вид а 12.

По окончании выполнения этой микрокоманды осуществляется переходв ячейку 572, в которой записана микрокоманда перехода к микроподпрограмме нормализации результата.

Последняя микрокоманда этой микропрограммы имеет вид а1 13.

По окончании выполнения этой микрокоманды осуществляется переход в ячейку 573.

Затем процессор передает результат в нужные регистры и переходит к выполнению микропрограммы выборки следующей команды.

При использовании микроподпрограммы нормализации результатов в команде сложе503240

Формула изобретения

Составитель Ю. Евдолюк

Техред Т. Курилко

Корректор А. Дзесова

Редактор T. Янова

Заказ 703/10 Изд. № 1098 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ния, имеющей, например, код 52, возврат из этой микроподпрограммы осуществляется в ячейку 523.

Таким образом, возврат из общих микроподпрограмм всегда осуществляется в зону выполнения той команды, которая осуществляет вход в данную микроподпрограмму.

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, регистр кода операции, блок управления, дешифраторы кода микрокоманды и кода ветвления соответственно, первый и второй элементы

«ИЛИ», первый, второй и третий элементы

«И», причем, выход блока памяти микрокоманд соединен со входом регистра микрокоманд, первый выход которого соединен через дешифратор кода микрокоманды с первым входом блока управления, второй выход регистра микрокоманд соединен со входом дешифратора кода ветвления, первый выход которого соединен со вторым входом блока управления, первый выход которого соединен с первым входом первого элемента «ИЛИ», второй вход которого соединен с третьим выходом регистра микрокоманд, четвертый выход которого соединен с первым входом первого элемента «И», второй вход которого соеди5 нен со вторым выходом блока управления и с первыми входами второго и третьего элементов «И», второй вход второго элемента «И» соединен с выходом регистра кода операции, а выход соединен с:первым входом второго

10 элемента «ИЛИ», второй вход которого соединен с выходом первого элемента «И», а выход соединен с первым входом регистра адреса, второй вход которого соединен с выходом третьего элемента «И», а выход — с вхо15 дом блока памяти микрокоманд, второй вход третьего элемента «И» соединен с выходом первого элемента «ИЛИ», о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно дополнительно содержит элемент «НЕ» и тре20 тий элемент «ИЛИ», первый вход которого шиной начала операции соединен с третьим выходом блока управления, второй вход шиной возврата соединен с вторым выходом дешифратора кода ветвления, а выход соединен

25 непосредственно с третьим входом второго элемента «И», а через элемент «НЕ» — с третьим входом первого элемента «И».