Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

Свез Соввтокнк

Соцналнстннесккк

Ресауйнк (61) Дополнительное к авт. свид-ву (22) Заявлено 25.01.74 (21) 1993023/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.02.76. Бюллетень № 6

Дата опубликования описания 27.05.76 (51) М. Кл. G 06F 13/00

Государственнык комитет

Совета й1нннстров СССР ло дЕлам нэооретений н открытий (53) УДК 681.325.36 (088.8) (72) Авторы изобретения

А. И. Иванов и Л. H. Корягин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИEA

Предлагаемое устройство относится к цифровой вычислительной технике и может быть использовано при построении вычислительных машин и систем.

Известны устройства для обмена информацией, содержащее регистры, первую группу элементов «И», вторую группу элементов

«И», дешифраторы считывания, дешифраторы записи, блок управления и группу элементов

«ИЛИ» по одной на каждый разряд передаваемой информации, входы каждого элемента

«ИЛИ» соединены с выходами элементов «И». первой группы соответствующего разряда, первые входы которых соединены с выходами соответствующих дешифраторов считывания, вторые входы соединены с выходами соответствующих регистров, выходы элементов

«ИЛИ» соединены с первыми входами элементов «И» второй группы, вторые входы которых соединены с выходами соответствующих дешифраторов записи, а выходы соединены с входами соответствующих регистров, входы дешифраторов записи и считывания соединены с выходом блока управления.

Недостатком известных устройств является относительно низкая нагрузочная спосооность. Нагрузочный резистор малой величины, являющийся общей коллекторной нагрузкой объединенных выходов вентилей считывания, определяет значительную часть коллекторного тока выходных транзисторов вентилей считывания. При формировании низкого уровня на линии ток, протекающий через нагрузочный резистор, является бесполезным и снижает нагрузочную способность вентилей считывания, Предлагаемое устройство отличается тем, что оно содержит управляемый запоминающий элемент, вход которого соединен с выхо1р дом блока управления, а выход — с входом элемента «ИЛИ».

Другим отличием предлагаемого устройства является то, что в нем управляемый запоминающий элемент содержит первый и второй

15 элементы «И — НЕ» и элемент «И», первый вход которого соединен с выходом первого элемента «И вЂ” НЕ», второй вход — с первым входом второго элемента «И вЂ” НЕ», а выход элемента «И» соединен со вторым входом вто20 рого элемента «И вЂ” НЕ», выход второго элемента «И вЂ” HE» соединен с входом первого элемента «И вЂ” НЕ», Это позволяет увеличить нагрузочную способность линии и ее пропускную способность.

25 Кроме того, введенные триггеры могут быть использованы как буферный регистр, управляющий выполнением некоторых операций

ЦВМ.

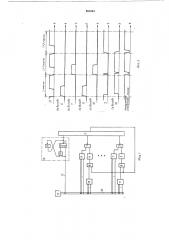

На фиг. 1 представлена блок-схема предлагаемого устройства. Она содержит первую

503244.

60 группу элементов «И» 1, 2, группу элементов

«ИЛИ» 3 по одной на каждый разряд передаваемой информации, регистры 4, 5, дешифраторы считывания 6, 7, вторую группу элементов «И» 8, 9, дешифраторы записи 10, 11, блок управления 12 с выходной шиной (магистралью) 13. Устройство также содержит управляемый запоминающий элемент 14, выполненный на логических элементах «И — HE» 15, 16.

Цепь обратной связи управляемого запоминающего элемента и его установочный вход

17 соединены со входами элемента «И» 18, выход .которого соединен с коллекторным входом расширения по «ИЛИ» элемента «И—

НЕ» 15.

На фиг. 2 представлена временная диаграмма, поясняющая работу устройства обмена.

Обозначения соответствуют обозначениям фиг. 1.

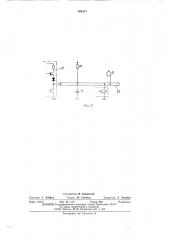

На фиг. 3 показана схема одной линии информационной магистрали. Выходной каскад

19 элемента 14 с тремя состояниями, выходной транзистор 20 элемента считывания с открытым коллекторным выходом, элементы записи 21 — распределенная емкость 22 линии 23 информационной магистрали и нагрузочный резистор 24 линии информационной магистрали, Предлагаемое устройство обмена информацией ра ботает следующим образом.

В начале каждого i-го такта (когда нужно производить перепись содержимого одного регистра на другой регистр) по входу 17 блок управления 12 посылает отрицательный импульс сброса запоминающего элемента 14.

Одновременно с этим комбинацией соответствующих импульсов на выходах, например, дешифраторов 6, 11 формируются соответственно импульс считывания содержимого регистра 4 и импульс записи информации на регистр 5.

Появляющийся на выходе элемента «И» 1 (на линии информационной магистрали) перепад уровня с высокого на низкий (предполагается, что в данном разряде регистра 4 хранится «единица») через элемент «И — HE»

16 управляемого запоминающего элемента

14, проинвертировавшись, поступает на вход элемента «И» 18. По концу отрицательного импульса (вход 17) управляемый запоминающий элемент 14 запоминает состояние низкого уровня линии информационной магистрали.

Расширенный таким образом импульс надежно «ловится» (стробнруется) выходным импульсом дешифратора 11 без увеличения длительности такта.

Когда на входе 17 элемента с тремя состояниями низкий уровень, его выходные транзисторы (верхний и нижний) находятся в закрытом состоянии. Это третье состояние элемента в дополнение известным двум состояниям, когда из двух выходных транзисторов один закрыт (открыт), другой открыт (закрыт) .

При формировании на линии перепада уровня с низкого на высокий (это происходит в начале такта, см. фиг. 2, такты i+1, i+2), кратковременно открывается верхний выходной транзистор элемента с тремя состояниями и подключает кратковременно параллельно к нагрузочному резистору линии ограничительный резистор выходного элемента. При этом происходит быстрый заряд распределенной емкости 22 линии.

При формировании на линии низкого уровня верхний выходной транзистор элемента с тремя состояниями всегда за крыт, и ток в этом случае определяется незначительным током через нагрузочный резистор и существенно большим током большого количества нагрузок (элементов записи).

Формула изобретения

1. Устройство для обмена информацией, содержащее регистры, первую группу элементов

«И», вторую группу элементов «И», дешифраторы считывания, дешифраторы записи, блок управления и группу элементов «ИЛИ» по одной на каждый разряд передаваемой информации, входы каждого элемента «ИЛИ» соединены с выходами элементов «И» первой группы соответствующего разряда, первые входы которых соединены с выходами соответствующих дешифраторов считывания, вторые входы соединены с выходами соответствующих регистров, выходы элементов «ИЛИ» соединены с первыми входами элементов

«И» второй группы, вторые входы которых соединены с выходами соответствующих дешифраторов записи, а выходы соединены с входами соответствующих регистров, входы дешифраторов записи и считывания соединены с выходом блока управления, о т л и ч а ющ е е с я тем, что, с целью увеличения нагрузочной способности и повышения быстродействия, оно содержит управляемый запоминающий элемент, вход которого соединен с выходом блока управления, а выход — с входами элементов «ИЛИ», 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что в нем управляемый запоминающий элемент содержит пер вый и второй элементы

«И — НЕ» и элемент «И», первый вход которого соединен с выходом первого элемента

«И — НЕ», второй вход — с первым входом второго элемента «И вЂ” НЕ», а выход элемента «И» соединен со вторым входом второго элемента «И вЂ” HE», выход второго элемента

«И — HE» соединен с входом первого элемента «И вЂ” HE».

503244

3 вр ю»

1

Составитель М. Аршавский

Техред М. Семенов

Редактор С. Хейфиц

Корректор Е. Хмелева

Типография. пп. Сапунова, 2

Заказ 1115/1 Изд, № 1173 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5