Формирователь импульсов на мдп-транзисторах

Иллюстрации

Показать всеРеферат

ш1503353

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 04.04.74 (21) 2012185/26-21 с присоединением заявки Ме (23) Приоритет

Опубликовано 15.02.76. Бюллетень Хо 6

Дата опубликования описания 14.07.76 (51) М. Кл. Н ОЗК 5/02 ЬСударстоекиый комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.142.07 (088.8) (72) Автор изобретения

А, Г. Солод (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к усилителям и может быть использовано в устройствах автоматики и вычислительной техники.

Известен формирователь импульсов на

МДП-транзисторах, содержащий последова- 5 тельную цепь, состоящую из зарядного транзистора, накопительного конденсатора, ключевого транзистора и включенную между шинами источника питания, причем затвор зарядного транзистора соединен с шиной источ- 10 ника питания, а затвор ключевого транзистора — с источником входного сигнала, нагрузочный транзистор, переход затвор-исток которого включен параллельно накопительному конденсатору. 15

С целью формирования последовательностей синфазных импульсов с разными амплитудами в предлагаемый формирователь дополнительно введены несколько последовательных 20 цепей и нагрузочных транзисторов, причем исток нагрузочного транзистора первой последовательной цепи соединен с затворами нагрузочных транзисторов последующих последовательных цепей, сток нагрузочного транзи- 25 стора последней последовательной цепи соединен с шиной питания, а стоки нагрузочных транзисторов предшествующих последовательных цепей соединены с истоками зарядных транзисторов, истоки нагрузочных транзисторов соединены с одной из обкладок соответствующих накопительных конденсаторов.

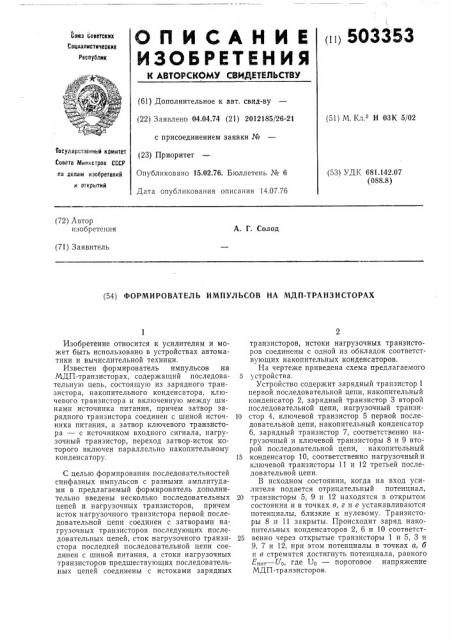

На чертеже приведена схема предлагаемого стройства.

Устройство содержит зарядный транзистор 1 первой последовательной цепи, накопительный конденсатор 2, зарядный транзистор 3 второй последовательной цепи, нагрузочный транзистор 4, ключевой транзистор 5 первой последовательной цепи, накопительный конденсатор

6, зарядный транзистор 7, соответственно нагрузочный и ключевой транзисторы 8 и 9 второй последовательной цепи, накопительный конденсатор 10, соответственно нагрузочный и ключевой транзисторы 11 и 12 третьей последовательной цепи.

В исходном состоянии, когда на вход усилителя подается отрицательный потенциал, транзисторы 5, 9 и 12 находятся в открытом состоянии и в точках в, г и е устанавливаются потенциалы, близкие к нулевому. Транзисторы 8 и 11 закрыты. Происходит заряд накопительных конденсаторов 2, 6 и 10 соответственно через открытые транзисторы 1 и 5, 3 и

9, 7 и 12, при этом потенциалы в точках а, б и в стремятся достигнуть потенциала, равного

Ео,— Uo, где 14 — пороговое напряжение

МДП-транзисторов.

503353 1к — Епнт1

U< — Ug — 2Епит Uo1 в 3Enaz 2 о а: 4Епит З 1о

Тираж 1029 Подписное

ЦНИИПИ Заказ 1504/5 Изд. ¹ 1168

Типография, пр. Сапунова, 2

С приходом на вход положительного перепада и установления на затворах транзисторов

5, 9 и 12 напряжения ниже порогового, последние закрываются и начинает увеличиваться потенциал в точке д, в точке а также возрастает отрицательный потенциал, составляющий сумму из уровня напряжения в точке в (Со) и напряжения на накопительном конденсаторе 2, которое равно Е „,— Up, при этом транзистор 1 закрыт, так как напряжение между его затвором и истоком меньше порогового напряжения Ua Uc Eïèò — Up.

При достижении напряжения в точке в значения, равного пороговому, транзисторы 8 и

11 открываются, потенциалы в точках г и е начинают возрастать, что приводит к увеличению отрицательного напряжения в точках б и д.

Увеличение отрицательного напряжения в точках б и д приводит к закрыванию транзисторов 3 и 7, исключая через них разряд конденсаторов 6 и 10, причем напряжение в точке д (U,) составляет сумму напряжений в точке е (U„) и напряжения на накопительном конденсаторе 10, которое равно Е гт — Уо. Напряжение в точке б составляет сумму из напряжения в точке г (U„) и напряжения на накопительном конденсаторе 6, которое также равно Е,— Up.

В установившемся режиме установятся следующие уровни напряжения в точках схемы

Эти уровни напряжений устанавливаются при работе схемы на высокоомную нагрузку и при малых значениях паразитных емкостей по сравнению с наполнительными конденсаторами. В случае, когда имеет место емкостная нагрузка C„„ и при равенстве емкостей конденсаторов б и 10, уровень выходного напряже5 ния определяется из выражения

U,„„= U, = (ЗЕ„„, — 2U,) ..

С+ С„ где С вЂ” суммарная емкость конденсаторов 6

10 и 8. С приходом отрицательного напряжения на вход устанавливаются потенциалы, соответствующие исходному состоянию.

Формула изобретения

15 Формирователь импульсов на МДП-транзисторах, содержащий последовательную цепь, состоящую из зарядного транзистора, накопительного конденсатора, ключевого транзистора и включенную между шинами источника пи20 тания, причем затвор зарядного транзистора соединен с шиной источника питания, а затвор ключевого транзистора соединен с источником входного сигнала, нагрузочный транзистор, переход затвор-исток которого включен па25 раллельно накопительному конденсатору, отл и ч а ю шийся тем, что, с целью формирования последовательностей синфазных импульсов с разными амплитудами, дополнительно введены несколько последовательных

30 цепей и нагрузочных транзисторов, причем исток нагрузочного транзистора первой последовательности цепи соединен с затворами нагрузочных транзисторов последующих последовательных цепей, сток нагрузочного транзистора

35 последней последовательной цепи соединен с шинами питания, а стоки нагрузочных транзисторов предшествующих последовательных цепей соединены с истоками зарядных транзисторов, истоки нагрузочных транзисторов сое40 динены с одной из обкладок соответствующих накопительных конденсаторов.