Многоканальная система формирования сложных нелинейных зависимостей

Иллюстрации

Показать всеРеферат

ОП ИСАние

Союз Соеетских

Социалистических

Ресвублик (i>) 504211

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 09.04.7 3 (21) 1903930/18-24 с присоединением заявки _#_e (23) Приоритет (43) Опубликовано25.02.76.Бюллетень Ph 7 (45) Дата опубликования описания31.03.76 (51) M. Кл.

G 06 J 1/00

Гвсударственнвй нвмнтвт

Соватв Мнннстров СССР нв днлам нзабретеннй

w юткрытнй (53) УДК 681.325. (088.8) H. И. Алимов, В. П. Боюн и Л, Г. Козлов (72) Авторы изобретения (71) Заявитель Ордена Ленина институт кибернетики АН Украинской ССР (54) МНОГОКАНАЛЬНАЯ СИСТЕМА ФОРМИРОВАНИЙ

СЛОЖНЫХ НЕЛИНЕИНЫХ ЗАВИСИМОСТЕИ

Изобретение касается вычислительной техники и может быть использовано для реализации нелинейных зависимостей в управляюших системах и гибридных вычислительных машинах. а

Известны многоканальные системы формирования сложных нелинейных зависимостей, содержашее эапоминаюший блок, входы которого соединены с выходами регистра адреса, другие выходы которого подсоединены ко 10 входам первого цифро-аналогового преобразователя, соединенного своим выходом со входами схем сравнения, другие входы которых подсоединены к выходам аналогового вычислительного блока, входы которого со- 15 единены с выходами второго цифро-аналогового преобразователя, выходы схем сравнения соединены со входами первой группы элементов И, логические схемы определения направления прирашений, соединенные 20 первыми входами с выходами первой группы элементов И, входы которой подсоединены а к выходам усилителей считывания, соединенных своими входами с выходами запоминаюшего блока, логические схемы определения 25 направления прирашений соединены вторыми входами с выходами триггеров двух младших разрядов регистра адреса, а выходысо входами второго цифро-аналогового преобразователя.

Однако для этих систем характерно: небольшое количество реализуемых устройством нелинейных зависимостей, поскольку оно ограничено количеством хранимых нелинейных зависимостей, которое соответствует разрядности запоминаюшего устройства, и в них невозможно использовать нелинейные зависимости, хранимые в запоминаюшем устройстве, для реализации на их базе более сложных нелинейных заьи имостей.

Иля расширения функциональных возможностей в систему введены блок управления, первый коммутатор, управляюший вход которого соединен с выходом блока управления, а информационные входы - с выходами усилителей считывания, вторая группа элементов И, соединенная входами с выходами первого коммутатора, а выходами — с первыми входами дополнительных логических схем определения направления прирашений, 5О421.i

»«торая группа схем сравнения, соединенная своимя входами с выхоаачи первого цифро »капогового преобразователя, а выходачи со входамя второй группы э.тементов И второй -коммутатор, управляющий вход котороае соединен с выходом блока управления, »«яформационны входы соединены с выходам» второго цифро-аналогового преобразователя, а выходы - со входами второй группы схем сравнения, третий цифро-ан..поговый

»реобразователь, входы которого соединены с выходами дополнительных логических схем сятределения направления приращений, соедявенных вторыми входами с выходами триггеро. . двух младших разрядов регистра адреса, а выходы третьего цифро-аналогового

И вреобразователя - с информационными входами второго коммутатора и выходами аналогового вычислительного блока.

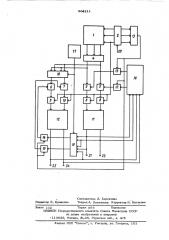

Схема предпоженнсФ системы преаст )влена на чертеже.

Она содерж»т запоминающий блок 1, регистр адреса 2, цпфро-аналоговый преобразователь 3, усилители считывания 4, первую и вторую группы элементов 5, 6 и 7, логические схемы определения направления приращения 8, 9, 10, второй цифро-аналоговый преобразователь 11, третий цифроаналоговый преобразователь 12, схемы сравнения 13, 14 и 15, аналоговый вычислиЗО тельный блок 16, блок управления 17, первый коммутатор 18 и второй коммут;;тор19, вход 20 регистра адреса 2.

Входы запоминающего блоха 1 соединены с выходами регистра адреса 2, другие «щ выходы которого подгчючены ко входам цифро-аналогового преобразователя 3, соединенного своим выходом со входами схем сравнения 13, другие входы которых подключены к выходам аналогового вычислитель-«О ного блока 16, входы которого соединены с выходами цифро-аналогового преобразователя 11. Первые входы логических схем определения направления приращения 8 соединены с выходами вентильных схем 5, 45

Выходы триггеров двух младших разрядов регистра адреса 2 соединены со вторыми входами логических схем определения направления приращений S, выходы которых соединены со вход64и цифро-аналогового пре-й() обраэователя 11. Выходы схем сравнения 13 соединены со входами вентильных схем 5, другие входы которых подключены к выходам усилителей считывания 4, соединенных своими входа .:и с выходами запоминающего И блока 1. Выход блока управления 17 соеди« яен с управляющим входом первого коммутатора 18, информационные входы которого подключены к выходам усилителей считывания 4, и с управляющим входом второго ком-60 ф мутатора 19а ннфорл«ационные входы котоРого пэдкпк чены к выходам цифро аналог вого преобразователя 11

Между выходами первого коммутатора 18

w входами аналогового вычислительного блока 16 включены аве цепочки включенных последовательно вентипьной схемы 6 (7), логической схемы определения направления превращений 9 (10), цифръ-аналогового пре« образоватепя 12. Выходы второго коммутат тора 19 соединены с первыми входами схем сравнения 14 и 15, вторые входы которых соединены с выходом цифрэ-аналогового преобразователя 3, а выходы схем сравнения 14 и 15 соединены со вторыми входами вентильных схем 6 и 7. Вторые входы логических схем определения направления приращения 9и 16 соединены с выходами триггеров двух младших разрядов регистра адрес..1 2, а выход цифро-аналогового преобразователя 12 подкпкчен к одному из информационных входов второго коммутатора 19. г

Раэрядность запоминающего блока 1 определяет количество нелинейных зависимостей которые выдаются на выходы 21 л 22. Кроме того, устройство позволяет реализовать сложные нелинейные зависимости первого

$ (f(X)J и второго Ч (% («(Х1)) типов, причем функции f Y и + . принадлежат множе» ! ству нелинейных зависимос тей, записанных в зап очи нающе л блоке 1.

Для реализации сложной зависимости первого типа необходимо с помощью первого коммутатора 18 подключить выход усилителя считывания 4, соответствующего функции т, к первому входу вентиля 6 или 7, & один из Bblxoaoa цифро-аналогового преобразователя соответствующий функции с помощью второго коммутатора 19 необходимо подключить к первому входу схемы сравнения 14 или 15. Тогда ф„-.кция f(X) будет выступать в роли аргумента и на выходе 23 или 24 получится искомая нелинейная зависимость первого типа +f (Х)). При реализации сложной нелинейной зависимости второго типа необходимо с помощью второго коммутатора 19 выход цифро-а. апогового преобразователя 11, на кото, ом получена нелинейная зависимость Р((Х)), подключить к первому входу схемы сравнения 15.

При помощи первого коммутатора 18 выход усилителя 4, соответствующего функции т, подключается к первому входу вентиля 7.

Теперь в роли аргумента выступает функция Ф (Х)), и на выходе 24 образуется иелииейиаи аависиыость второго тиаатт уцй1), При наличии в запоминающем блоке 1т базовых нелинейных зависимостей предлагаемая система позволяет реализовать тт (и-2) fn

504211 видов разнообразных нелинейных зависимостей.

Ф ормула изобретен ия

Многок.нальная система формирования сложных нелинейных зависимостей, содержашая эапоминаюший блок, входы которого соединены с выходами регистра адреса, другие выходы которого подсоединены ко входам пер вого цифрэ-аналбгового преобразователя, со единенного своим выходом со входами схем сравнения, другие входы которых подсоединены к выходам аналогового вычислительного блока, входы которого соединены с выходами к второго цифро«аналогового преобразователя, выходы схем сравнения соединены со входами первой группы элементов . И, логические схемы определения направления прирашений, соединенные первыми входами с выходами О первой группы элементов И, входы которой подсоединены к выходам усилителей считывания, соединенных своими входами с выходами запоминаюшего блока, вторыми входа» ми логические схемы определения направле- I ния прирашений соединены с выходами двух младших разрядов регистра адреса, а выходами - co входами второго цифро-аналогового преобразователя, о т л и ч а ю ш а я—

6 с я тем, что, с целью расширения функциональных возможностей, она содержит блок управления, первый коммутатор, управляюший вход которого соединен с выходом блока управления, а информационные входы - с выходами усилителей считывания, вторую группу элементов И, соединенную входами с выходами первого коммутатора, а входа,ми - с первыми входами дополнительных ,логических схем определения направления .прирашений, схемы сравнения, соединенные !, своими входами с выходами первого цифро,аналогового преобразователя, а выходами

,— со входами второй группы элементов И, второй коммутатор, управляюший вход которого соединен с выходом блока управления, информационные входы соединены с

:выходами второго цифро-аналогового пре,образователя, а выходы - со входами схем сравнения, третий цифро-аналоговый пре образователь, входы которого соединены

;.с выходами дополнительных логических схем определения направления приращений, соединенных вторыми входами с выходами триг геров дьух младших разрядов регистра ад,реса, а выходы третьего цифро-аналогово1го преобразователя с информационными вхо.дами второго коммутатора и входами аналогового вычислительного блока.

Ф

Редактор Е. Кравцова

Составитель Л. Захматова

Техред А. Демьянова Корректор H. Бугакова

Заказ g pg Тираж g64 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж«35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Гагарина, 101