Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

О П И C" А "Н -"И Е

Союз Советских

Социалистических

Республик (11) с 504250

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ

@+* (61) Дополнительное к авт. свид-ву (51) И. Кл.

G11 С 20/00 (22) Заявлено10.01.75 (21) 2095263/18-24 с присоединением заявки №(23) Приоритет (43) Опубликовано25.02.76.Бюллетень № 7

> (45),".ата опубликования описания 25 0д 76

Государственнь!й комитет

Совета Министров СССР оа диан изобретений и отхрытий (53) УДК

681.327 (088.8) (72) Авторы изобретения

Н. И. Вариес, Б. Е. Гласко и А. К„ Култыгин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПАМЯТИ

Изобретение относится к зал з .нающим

T устройствам.

Известно устройство для контроля блоков памяти, содержащее блок формирования адресов, подключенный к выходным шинам устройства, блок анализа, соединенный с блоком сравнения и блоком регистрации, Известное, устройство для контроля одноразрядных блоков памяти с дефектами производит сортировку одноразрядных блоков па- щ мяти для получения полноразрядного блока памяти по признаку несовпадения адресов ячеек, содержащих дефекты по всему полноразрядному блоку памяти, Однако оно требует дополнительной опе 15 рации — точной маркировки дефектов и ие обеспечивает автоматизации процесса сор тировки блоков памяти с исправлением ошибок, требует больших затрат оборудования.

Кроме того это устройство не обеспечивает 20 ко)птлектования одноразрядных блоков памя,ти в полноразрядные блоки памяти, что существенно снижает область его применения.

11ель изобретения — расширение области ! применения устройства. И

Устройство содержит блоки памяти, адресные входы которых подключены к блоку формирования адресов, первые управляющие

: входы - к выходу блока регистрации, второй

1 управляющий:вход.первого блока памяти -к выходу второго блока памяти, второй управ ляющий вход которого соединен с выходом первого блока памяти и со входом блокт», регистрации, а третий управляющий вход первого блока памяти подключен к выходу блока сравнения.

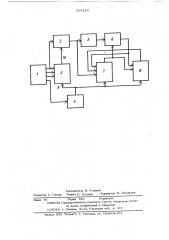

На чертеже: блок-схема устройства, Устройство содержит блок управления 1,, блок сравнения 2, ттроверяемый одноразряд ный бчок памяти 3, блок формирования ад. ресов 4, блок аналяэа 5 для определения

, количества ошибок, блок регистрации 6, первый 7 и второй 8 блоки памяти. Адресные входы блоков 7 и 8 соединены с соответ ствующими выходами блока формирования адресов 4, первые управляющие входы с

I выходом блока регистрации 6, второй уп равляющий вход первого блока памяти 7—

< ,с выходом второго блока т амятн 8, вто рой управляющий вход второго блока плмя50М2"".0 ти 8 — с выходом первого блока памяти 7

*,;,c входом блока регистрации 6, а третий управляющий вход первого блока памяти 7 соединен с выходом блока сравнения 2.

Проверяемый блок памяти подключен к выходным 9 и входным 10 шинам устройства.

Устройство работает следующим образом, Перед началом контроля и сортировки проверяемых одноразрядных блоков памяти щ

3 предварительно записывается в блоки 7 и 8 "0 по всем адресам, после чего блок формирования адресов 4 устанавливается в "0".

При пуске устройства блок формирова- ц ния адресов 4 вырабатывает сигналы, обеспечивающие перебор всех адресов проверяемого одноразрядного блока памяти 3, Блок правления 1 при первом пересче»те адресов формирует на числовых шинах gp записи импульсы числа, соответствующие записи 1 и "О" по каждому адресу, а на управляюших шинах записи и считываниясоответствуюшие импульсы записи и считывания. С выхода проверяемого однораз- 25 рядного блока памяти 3 сигнал поступает на первый вход блока сравнения 2, второй вход которого соединен с числовой шиной записи.

В случае возникновения ошибки в про- ЗО веряемом одноразрядном блоке памяти 3 сигнал блока сравнения 2 поступает на блок анализа 5, а также на управляющий вход первого блока памяти 7. Блок анализа 5 вырабатывает сигнал, возбуждающий блок регистрации 6, если число ошибок превышает заданное количество, а матрйца считается "негодной для данного полноразрадного блока памяти и откладывается.,э массив одноразрядных блоко.- памяти, которые будут участвовать в сортировке для- следующих полнораэрядных блоков памяти, Одновременно, наличие сигнала с блока сравнения 2 на управляющем входе блока 45

7 приводит к считыванию из него информации и записыванию "1 по адресу, где произошел отказ в проверяемом блоке 3, Если при этом из блока 7 считывается

0", что соответствует отсутствию ошибО бок по этому адресу в ранее проверенных одноразрядных блоках памяти, то блок 6

4 не возбуждается. Если же считывается из блока 7 "1", что означает наличие ошибки по этом -адресу в одном из проверенных ранее одноразрядных блоках памяти, то возбуждается блок 6 и проверяемый одноразрядный блок 3 считывается "негодным" для данного полноразрядного бло ка памяти и возвращается в массив одноразрядных блокбв памяти, которые будут участвовать в сортировке для следующих полноразрядных блоков памяти.

В тех случаях, когда проверяемый блок

3 не годен для подбираемой партии полноразрядного блока памяти, в блоке 7 произойдет искажение информации об ошибках по адресам полноразрядного блока памяти.

Эта информация должна быть восстановлена.

Восстановление информации в блоке 7 происходит при повторном переборе всех адресов, При этом с блока 6 на управляющих входах блоков 7, 8 формируется сигнал> приводящий к считыванию из блока 8 и к записи в блок 7 по всем адресам.

В блок 7 записывается информация, считанная из блока 8.

Если проверяемый блок 3 годен, то с блока 6 на управляющих входах блоков 7 и 8 формируется сигнал, приводящий к считыванию из блока 7 и к записи в блок 8 по всем адресам, В блок 8 записывается информация, считанная из блока 7, Формула изобретения

Устройство для контроля блоков памяти, содержащее блок формирования адресов, подключенный к выходным шинам устройства, блок анализа, соединенный с блоком сравнения и блоком регистрации, о т л и— ч а ю ш е е с я тем, что, с целью расширенин области применения устройства, оно содержит блоки памяти, адресные входы которых подключены к блоку формирования адресов, первые управляющие входы — к выходу блока регистрации, второй управляю щий вход первого блока памяти — .. выходу второго блока памяти, второй управляющий вход которого соединен с выходом первого блока памяти и со входом блока регистра» ции, а третий управляющий вход первого блока памяти подключен к выходу блока сравнения.

504250

Составитель B. Рудаков

Редактор F.. Гончар Техред Q, дуговая Корректор И. Зинзикова

Заказ 76 Тираж 723 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, r. Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Гагарина,101