Цифровой фазовый компаратор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Ресяубпик т11) 5О4293.

1

1 ( с (61) Дополнительное к авт. свид-ву—

{22) Заявлено 17.04 74.(21) 2017740/26-21 с присоединением заявки № (23) Приоритет(51) M. Кл.

Н 03 В 1 3/00

Государстаенна и камнтет

Совета Мнннстров СССР по делам нэооретеннй н открытнй (43) Опубликовано 25.02,76. Бюллетень № 7 (53) УДК 621„ 373 (088.8 (45) Дата опубликования описания (72) Авторы изобретения

В, В, Быданов и С. П. Корнеев (71) Заявитель (54) Циф»- ОВОИ 4 ДЗОВЫй КОМПАРЛтО(Изобретение относится к импульсной технике.

Известен цифровой фазовый компаратор, содержащий блок выделения разности фаз, на входы которого поданы сигналы входной и эталонной частоты, а выходы которого подключены к входам элемента "ИЛИ", и триггер. Известный цифровой фазовый компаратор имеет недостаточную точность определения направления изменении фаз.

Целью изобретения является повышение точности определения направления изменения фаэ.

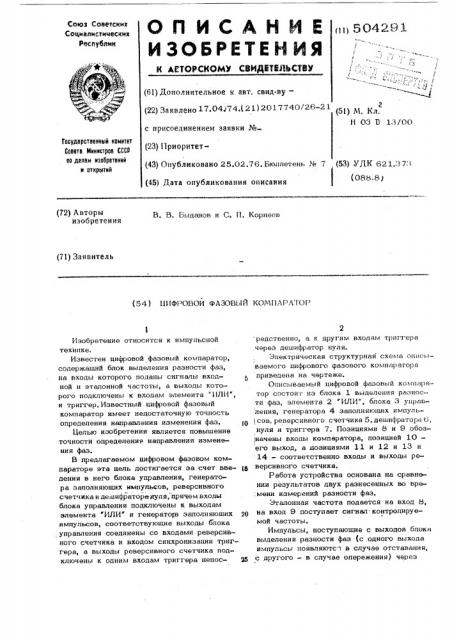

В предлагаемом цифровом фазовом компараторе эта цель достигается за счет введения в него блока управления, генератора заполняющих импульсов, реверсивного счетчика и дещифраторануля, причем входы блока управления подключены к выходам элемента "ИЛИ" и генератора заполняющих импульсов, соответствующие выходы блока управления соединены со входами реверсивного счетчика и входом синхронизации триггера, а выходы реверсивного счетчика подключены к одним входам триггера непос редственно, а к другим входам триггера через дешифратор нуля, Электрическая структурная схема описиваемого цифрового фазового компаратора приведена на чертеже.

Описываемый цифровой фазовый компаратор состоит из блока 1 выделения разности фаз, элемента 2 "ИЛИ", блока 3 управления, генератора 4 заполняющих импульI сов, реверсивного счетчика 5, дешифратора 6, нуля и триггера 7. Позициями 8 и 9 обоз,.начены входы компаратора, позицией 10— его выход, а позициями 11 и 12 и 13 и

14 — соответственно входы и выходы реверсивного счетчика.

Работа устройства основана на сравнении результатов двух разнесенных во вре;мени измерений разности фаз.

Эталонная частота подается на вход И, на вход 9 поступает сигнал контролируемой частоты.

Импульсы, поступающие с выходов блока выделения разности фаэ (с одного выхода импульсы появляютс т в случае отставания, ча с другого - в случае опережения) через 04291

Составитель А. Артюх

Редактор О. Кузнецова Техред М, Ликович Корректор В. Микита

Заказ 91 Тираж 1029 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Гагарина, 101 элемент " ИЛИ" на вход блока управления, заполняются сигналом с частотой генератора заполняющих импульсов и подаются на реверсивный счетчик, причем первый (заполненный) импульс поступает на вход

11 (сложение"), а каждый И -ный (в данном случае второй) на вход 12 ("вычитание"). По окончании процесса вычитания с выхода блока управления на синхронизирующий вход триггера и на вход сбро- ip са реверсивного счетчика подается сигнал, устанавливающий триггер в положение, определяемое состоянием последнего разряда реверсивного счетчика, выходы которого соединены с входами данного триггера, 1 а реверсивный счетчик — в исходное нулевое состояние, подготавливая его тем самым.. к следующему измерению.1

В исходном состоянии счетчика на выходе 13 будет нулевой потенциал и на выходе 14 соответственно - высокий„

И случае, когда количество поступивших импульсов на вход 11 "сложение" реверсивного счетчика будет больше числа импульсов, поступивших на вход 12

"вычитание", состояние выходов 13 и 14 не изменится, в обратном же случае при переходе нуля счетчик установится в единичное состояние и на выходах 13 и

I 14 к моменту считывания будут потенциалы обратные исходным, т.е. "1" и "О" соответственно, и триггер также изменит свое состояние на обратное, а именно на его выходе будет высокий потенциал.

При равенстве числа импульсов, пос35 тупивших.на вход 11 "сложение" реверсивного счетчика, числу импульсов, поступивших на вход 12,"вычитание", счетчик установится в нулевое состояние и на выходе дешифратора нуля появится сигнал, поступивший на вторые входы "триггера, .1 запрещающие его: переключение.

Таким образом, на выходе цифрового фазового комларатора в случае увеличения.:разности фаз входных сигналов будет низкий потенциал ("О" ), ьри уменьшении - высокий (" 1 " ) .

При постоянстве разности фаз за время измерения выходной сигнал сохраняет свое предыдущее состояние.

Формула изобретения

Цифровой фазовый компаратор, содержащий блок выделения. разности фаэ, на входы которого поданы сигналы входной и эталонной частоты, а выходы которого подключены к входам элемента "ИЛИ", и триггер, отличающийся тем, что, с целью повышения точности определения направления изменения фаз, в него введены блок управления, генератор заполняющих импульсов, реверсивный счетчик и дешифратор нуля, причем входы блока управления подключены к выходам эле-. мента "ИЛИ" и генератора заполняющих импульсов, соответствующие выходы блока управления соединены со входами реверсивного счетчика и входом синхронизации триггера, а выходы реверсивного счетчика подключены к одним входам триггера непосредственно, а к другим входам триггера — через дешифратор нуля.