Аналоговый нормализатор сигнала

Иллюстрации

Показать всеРеферат

ОП И

Союз Советских

Социалистических

Республик (11) 8 О4 ЗОВ (61) Дополнительное к авч. свид-ey(22) Заявлено 16.08.74 (21} 2053182/18-24 с присоединением заявки (23) Приоритет (43) Опубликовано25.02.76.Бтоллетень № 7 (45) Дата опубликования описания 12.04 76 (51} М. Кл.

Н О4 В 1(10

Государственный ноинтет

Совата Мнннатроа СССР по долаи иэооретеннй и открытий (Р) УДК 681.333:

;бф 9.2 (088.8) (72) Автор изобретения

О, М. Салтыковский (71} Заявитель (54) АНАЛОГОВЫЙ НОРМДЛИЗАТОР СИГНАЛА

Изобретение относится к кибернетике и может быть использовано при конструировании автоматов распознавания временных функций, работаюших в реальном масштабе времени, таких, например, как автоматы распознавания радиапокационных и гидролокеционных сигналов.

Известные аналоговые нормализаторы сигнапа, содержашие линию задержки, подключенную входом к источнику сигнада, и блок деления, це могут быть использованы sустр,ойствах для распознавания сигналов (функций времени) в шумах. Это обьясияется те:, ло в них отсутствуют блоки, которые могли бы обнаруживать сигнал и одновременно определять его по ложение в шумах.

Ueab изобретения — повышение точности работы, т.е. нормализация сигнала в шумах, независимая от его временного положения.

Для этого предлагаемый аналоговый иормализатор содержит сумматор, входы которого подключены соответственно к выходам линии задержки, средний выход кот%пи ВсЧЖлю юн к в оду числителя бло- ка деленная @ ФйхОА сумм@тора соединен .со Можем жамеиателя блока деления, соединенного с щ иодом устройства.

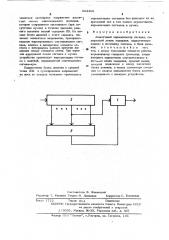

5 На чертеже показана блок-схема предлагаемого устройства.

Нормализатор содержит блок деления

1 аналоговых сигналов, линию задержки

2 со многими отводами и аналоговый сум16 матор 3, число входов которого совпадает с числом отводов линии 2. Вход числителя блока деления 1 подключен к среднему отводу 2, а вход знаменателя - к выходу сумматора 3.

И Подлежаший нормализации сигнап поступает иа вход линии задержки (ЛЗ) 2. Через временной интервал, равный половине полной задержки линии, сигнал появляется на выходе блока 1 деления напряжений.

20 Полное время задержки сигнапа выбирается в два раза большим максимального значения длительности нормализуемых сигналов.

В момент появления сигнала на входе .чиснителя блока деления 1 на входе i.зна

504305

Составитель В. Жовинский

Редактор Т. Иванова Техред М. Левицкая Корректор С. Болдижар

Заказ 1722 "иРаж 864 Подписное

ЦПИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал IIIiiI "Патент, г.Ужгород, ул. Гагарина, 101 менателя суммарное напряжение дости- 1 гает своего максимального значения, которое сохраняется постоянным (при от сутствии шумов) в течение времени, равного половине полной задержки ЛЗ. На выходе блока деления с етого момента начинает появляться напряжение, пропорциональное нормированным составляющим сигнала, взятым в дискретные моменты отсчета с интервалоь равным времени задержки между отводами линии. При наличии аддитивной смеси сигнала с шумом устройство производит нормализацию сигнала с ошибкой, определяемой соотношением сигнал-шум.

Подключение блока деления к средней точке ЛЗ2 и суммирование напряжений на всех ее отводах позволяет производить нормализацию сигналов без фиксации их на временной оси и тем самым осуществлять нормализацию сигналов в шумах.

Формула изобретения

Аналоговый нормализатор сигнала, содержащий линию задержки, подключенную входом к источнику сигнапа, и блок деления, отличающийся тем, что, с целью повышения точности работы, нормализатор содержит сумматор, входы которого подключены соответственно к вы.". ам линии задержки, средний выход которой подключен к входу числителя блока деления, а выход сумматора соединен со входом знаменателя блока деления, соединенного с выходом устройства.