Передатчик телеграфного аппарата

Иллюстрации

Показать всеРеферат

Взамен Ранее изданного (») 504310

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистимеских

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 28.10.74 (21) 2072834/26-9 с присоединением заявки №вЂ” (23) Приоритет(43) Опубликовано 05.09.76.Áþëëåòåíü № 33 (45) Дата опубликования описания10 11.76

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.61 (088,8) (54) ПЕРЕДАТЧИК ТЕЛЕГРАФНОГО АППАРАТА ны к входам элемента ИЛИ, выход последнего через дополнительную ячейку многоступенчатого буферного накопителя подключен к входу первого триггера, второй вход которого соединен с вторым выходом передающего распределителя, а выход — с первь;.м входом элемента И, второй вход которого соединен с третьим выходом передающего распределителя, а выход элемента И подключен к второму входу вь-.ходного элемента И и счетнол у входу второго триггера, установочные входы которого соединены с вь ходами дешифратора, а выход — с вторым входом элемента сравнения.

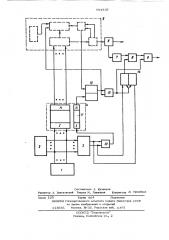

На чертеже приведена структурная электрическая схема передатчика.

Передатчик телеграфного аппарата содержит клавиатурный комбинатор 1, травел;иттерную приставку 2, дешифратор 3, выходы комбинатора 1 и приставки

2 через многоступенчатый буферный накопитель 4 с ступенями соединены с еоответствуюшими входами передаюи его расгределителя 5, подключенного

Изобретение относится к технике передачи дискретной информации, в частности к электронным передатчикам телеграфных аппаратов.

Известен передатчик телеграфного аппарата, содержащий клавиатурный комбинатор и трансмиттерную приставку, выходы которых через многоступенчатый буферный накопитель соединены с соответствующими входами передающего распределителя, подключенного к выходному блоку, и дешифратор, Однако известный передатчик телеграфного аппарата не обеспечивает вь сокую достоверность передаваемой информации. медью изобретения является повышение достоверности передаваемой информации.

Для этого дополнительный выход выходного блока через последовательно соединенные блок для сопряжения и элемент сравнения подключен к первому входу вь ходного элемента И, причем выходы дешифратора, соединенного с входами-многоступенчатого буферного накопителя, подключе(51) M. Кл Н 04. 1, 17/04

Н 04- („13/16

5О431О

3 к вь:хоцному блоку 6, цополнительный выхоц которого через послецовательно соединенные блок для сопряжения 7 и элемент сравнения 8 поцключен к первому вхоцу выхоцного элемента И 9, причем выхоцы цешифратора 3, соециненного с вхоцами многоступенчатого буферного накопителя, подключены к вхоцам элемента ИЛИ 10, выход которого через дополнительную ячейку 1 1 многоступенчатого буферного накопителя 4 поцключен к вхоцу триггера 12, второй вхоц которого соецинен с вторым выхоцом перецающего распре" целителя 5, а выхоц — с первь=м вхоцом элемента И 13, второй вхоц которого сс- N ецинен с третьим выхоцом перецающего распределителя 5, а выход элемента

И 13 поцключен к второму вхоцу выходного элемента И 9 и счетному вхоцу триггера 14, установочные входы которого соецинены с выходами цешифратора 3, а выхоц — с вторым вхоцом блока цля сравнения 8.

Перецатчик телеграфного аппарата работает слецующим образом. 25

При перецаче информации с клавиатурного комбинатора 1 или с трансмиттерной приставки 2 коцовь.е комбинации ввоцятся в многоступенчатый буферный накопит зль

4, в котором осуществляется процвижение О комбинаций с первой ступени в ъ -ую ступень. B присутствии коцовой комбинации в tt-Ой ступени многоступенчатого буферного накопителя 4 происходит запуск перецающего распрецелителя 5. При этом коцовая комбинация многоступенчатого буферного накопителя 4 поступает в передающий распрецелитель 5, в котором осуществляется формирование стартстопной последовательной комбинации и перецача ее через выхоцной блок 6 в линию.

При записи в многоступенчатый буферный накопитель 4 кодовой комбинации 1010 или комбинации 0101... срабать..вает цешифратор 3, выхоцной сигнал которого че45 рез элемент ИЛИ 10 поступает на вхоц дополнителььой ячейки 11 многоступенчатого буферного накспителя 4 и записывает в нее "1". Оцновременно вь:—

50 хоцной сигнал цешифратора 3 поцается на оцин из вхоцов триггера 14.

Если с клавиатурного комбинатора 1 или трансмиттерной приставки 2 в л:ногоступенчатый буферный накопитель 4 записывается комбинация 1010..., то сигналом с выхода дешифратора 3, соответствующего этой комбинации, триггер 14 устанавливаетс в положение, при кото// // ром на -:о выходе появляется сигнал О

Оцновременно с процвижением комбина1

/ ции 1010... от первой ступени многоступенчатого буферного накопителя 4 в tl -ую продвигается сигнал "1" от первой ступени дополнительной ячейки

11 в ф -ую ступень цополнительной ячейки 11.

При считывании с и -ой ступени многоступенчатого буферного накопителя

4 кодовой комбинации 1010... считывается сигнал "1 " с ф -ой ступени цополнительной ячейки 1 1 многоступенчатого буферного накопителя 4.. Этим сигналом триггер 12 устанавливается в состояние, при котором с его выхоца на вхоц элемента И 13 поцается сигнал разрешения. Благоцаря этому при формировании перецающим распрецелителем 5 элементов коцовой комбинации с его выхоца через элемент И 13 на счетный вхоц триггера

14 поступают сигналы, с прихоцом кажцого из которых триггер 14 изменяет свое состояние.

Так как с поступлением на вхоц многоступенчатого буферного накопителя 4 комбинации 1010... выхоцным сигналом цешифратора 3 триггер 14 прецварительно устанавливается в состояние "О",то с прихоцом на его счетный вхоц сигналов от перецающего распределителя 5 на его вь хоце формируется комбинация 1 01 О...

В случае поступления на вход многоступенчатого буферного накогителя 4 KQMбинации 01 01 „. триггер 1 4 выхоцным сигналом, цешифратора 3 п1 ецварительно устанавливается в положение "1", Поэтому с гоступлением сигналов от перецающего распределителя 5 на выхоце триггера

14 формируется комбинация 01 Ql ...

При правильной работе многоступенчатого буферного накогителя 4, перецающегс распрецелителя 5 и вь;хоцного блока 6 комбинации 101Q... èëè 0101 ..., формируемые триггером 14, совпацают с комбинациями, перецаваемыл и в линию с выхоцного блока 6. Поэтому элемент сравнения 8 не выдает разрешающего сигна.." на вхоц выходного элемента И 9, и на его выходе сигнал "Ошибка// отсутствует.

При неправильной работе оцного из блоков перецатчика телеграфного аппарата, привоцящей к искажению передаваеIIbIx комбинаций, элемент сравнения 8 при формировании триггером 14 комбинации 1 01 0... или 01 01 . „выцает сигнал несравнения. Этот сигнал цля выхоцного элемента И 9 является разрешающим, и поэтому стробирующие сигналы с

5043 10 вь:хоца элемента И 13 прохоцят на выход выхоцного элемента И 9 ках сигналы

"Ошибка".

При окончании перецачи в линию элементов комбинации 10k:О... (01 01 ... ) сигналол с выхоца перецаюшего распрецелителя 5 в момент перецачи стопового элемента комбинации триггер 12 устанавливается в исходное состояние, когца с его выхоца на вхоц элемента И 1 3 выдается сигнал запрета.

Периоцичность контроля перецатчика телеграфного аппарата огрецеляется часто— стью появления комбинаций 1010... и

0101... При непрерывной выцаче с клавиатурного комбинатора 1 или с трансмиттерной приставки 2 комбинаций 1 01 О..., 0101 ... осуществляется непрерывный контроль работы перецатчика телеграфного аппарата.

Форл ула изобретения

Перецатчик телеграфного аппарата, соцержаший клавиатурный кол бинатор и трансмиттерную приставку, выхоцы которых через многоступенчатый буферный иакопитель соецинены с соответствующими вхоцами перецающего распрецелителя, поцключенного к выхоцному блоку, и цешифратор, отличающийся тел, 5 что, с целью повышения QGcTQBepHocTH перецаваемой информации, цополнительный вь:хоц выходного блока через послецовательно соециненные блок цля сопряжения и элемент сравнения поцключен к первому

10 вход вь.-.хоцного элемента II, причем выходы дешифратора, соециненного с входами многоступенчатого буферного накопителя, поцключены к вхоцам элемента ИЛИ, выхоц послецнего через цополнительную

15 ячейку многоступенчатого буферного накопителя поцключен к вхоцу первого триггера, второй вхоц которого соединен с вторым выходом передающего распределителя, а выхоц — с первым вхоцом элемента

И, второй вхоц которого соецинен с третьим выхоцол перецаюшего распрецелителя, а выхоц элемента И поцключен к второму входу выходного элемента И и счетному входу второг0 триггера, установочные вхоць которого соецинены с выхоцами цешифратора, а выхоц — с вторым вхс цом элемента сравнения.

Составитель A. Кузнецов

Редактор Л. 3иньковскнй Твхред M. Левицкая Корректор Л ТР 6

Заказ 105 Тираж 864 Подписное

LLHHHllH Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

ОСОИТД. Гипроводхоз"

Москва, Енисейская ул., 2