Логический элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИ

ИЗОБРЕТЕН И

i1 50513l

Союз Советских

Соыиалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 03.01.73 (21) 1873968/26-21 с присоединением заявки № (32) Приоритет

Опубликовано 28.02,76. Бюллетень № 8

Дата опубликова ния описания 22,04.76

1) M. Кл. Н ОЗК 19/00

Государственный комитет

Совета Министров СССР

3) УДК 681.142 07 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. H. Поляков и Л. С. Элькин (71) Заявитель (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к автоматике и может применяться в различных электросхемах, содержащих суммирующие пороговые элементы с потенциальными входами.

Известен логический элемент, содержащий схему сравнения, вход которого через и резисторов подключен к и входным клеммам.

С целью повышения стабильности работы в предлагаемый элемент дополнительно введены и диодов и резисторы, причем каждая точка соединения резистора и входа схемы сравнения подключена через последовательно включенные диод и первый дополнительный резистор к нулевой шине, а общая точка диода и первого дополнительного резистора через второй дополнительный резистор соединена с входной клеммой.

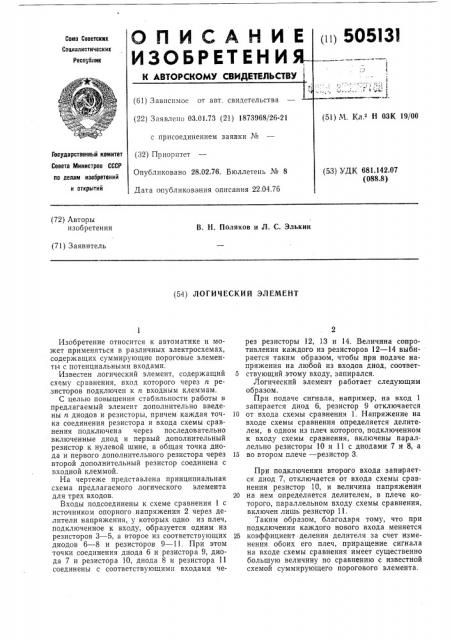

На чертеже представлена принципиальная схема предлагаемого логического элемента для трех входов.

Входы подсоединены к схеме сравнения 1 с источником опорного напряжения 2 через делители напряжения, у которых одно из плеч, подключенное к входу, образуется одним из резисторов 3 — 5, а второе из соответствующих диодов 6 — 8 и резисторов 9 — 11. При этом точки соединения диода б и резистора 9, диода 7 и резистора 10, диода 8 и резистора 11 соединены с соответствующими входами через резисторы 12, 13 и 14. Величина сопротивления каждого из резисторов 12 — 14 выбирается таким образом, чтобы при подаче напряжения на любой из входов диод, соответ5 ствующий этому входу, запирался.

Логический элемент работает следующим образом.

При подаче сигнала, например, на вход 1 запирается диод б, резистор 9 отключается

10 от входа схемы сравнения 1. Напряжение на входе схемы сравнения определяется делителем, в одном из плеч которого, подключенном к входу схемы сравнения, включены параллельно резисторы 10 и 11 с диодами 7 и 8, а

15 во втором плече — резистор 3.

При подключении второго входа запи рается диод 7, отключается от входа схемы сравнения резистор 10, и величина напряжения

20 на нем определяется делителем, в плече которого, параллельном входу схемы сравнения, включен лишь резистор 11.

Таким образом, благодаря тому, что при подключении каждого нового входа меняется

25 коэффициент деления делителя за счет изменения обоих его плеч, приращение сигнала на входе схемы сравнения имеет существенно большую величину по сравнению с известной схемой суммирующего порогового элемента.

505131

Формула изобретения

ВХОИ 2 РХОдЗ

ВХОд 7

Составитель А. Кузнецов

Техред E. Подурушина

Корректор Н. Стельмах

Редактор Е. Караулова

Заказ 837/14 Изд. № 116I Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Логический элемент, содержащий схему сравнения, вход которой через п резисторов подключен к и входным клеммам, отличаю шийся тем, что, с целью повышения стабильности работы, дополнительно введены и диодов и резисторы, причем каждая точка соединения резистора и входа схемы сравнения подключена через последовательно включенные диод и первый дополнительный резистор к нулевой шине, а общая точка диода

5 и первого дополнительного резистора через второй дополнительный резистор соединена с входной клеммой.